# Test und Verlässlichkeit Foliensatz 6: Hardware-Test und Selbsttest.

Prof. G. Kemnitz

Institut für Informatik, TU Clausthal 20. Januar 2025

#### Inhalt Foliensatz 6

| D | IC-l | Fe | h | lei |  |

|---|------|----|---|-----|--|

|   |      |    |   |     |  |

- 1.1 Fertigungsfehler

- 1.2 Praxistaugliche Fehlermodelle

- 1.3 IDDQ-Test

- 1.4 Untersuchung einiger Beispielfehler

- 1.5 Veraltetet Testvollständigkeitsmaße

#### Testsuche

- 2.1 Fehlersimulation

- 2.2 D-Algorithmus

- 2.3 Implikationstest

- 2.4 Suchraumstrukturierung

- 2.5 Komplexe

- **Funktionsbausteine**

- 2.6 Sequentielle Schaltungen

- 2.7 Speichertest Selbsttest

- 3.1 Pseudo-Zufallsregister

- 3.2 Signaturregister

- 3.3 Selbsttest mit LFSR

- 3.4 Fehlerorientierte Wichtung

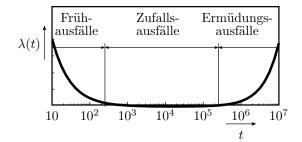

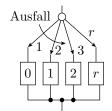

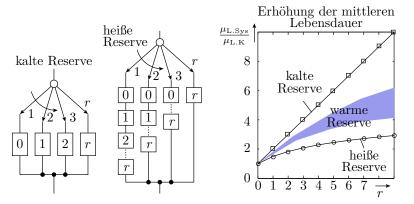

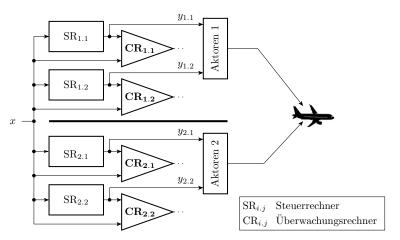

- 3.5 RAM-Selbsttest Baugruppentest Ausfälle

- Kenngrößen

- 5.2 Voralterung

- 5.3 Reparatur und Wartung Ausfalltoleranz

- Reserveeinheiten

- 6.2 KooN-Systeme

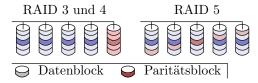

- 6.3 RAID und Backup

#### 6.2 Auf diesem Foliensatz

Die aus Testsicht kompliziertesten und anspruchsvollsten Systeme, aber auch die, mit denen es die meisten Erfahrungen gibt, sind hochintegrierte digitale Schaltkreise. Der Foliensatz behandelt hierzu:

- tatsächliche Fehler, Fehlermodelle und Erfahrungen, was sich bewährt hat und was nicht.

- Fehlersimulation, Testberechnung, prüfgerechter Entwurf,

- Lösungen für den Selbsttest.

Andere Bereiche, insbesondere Software, können von den mit Hardware gesammelten Erfahrung lernen.

#### Weitere Themen:

- Baugruppentest,

- Ausfallverhalten, Wartungstests und Redundanzen.

### 6.3 Wiederholung einiger Begriffe

Dynamische Tests sind in der Regel nur für eine winzige Stichprobe der möglichen Eingaben durchführbar. Auswahl der Testeingaben:

- gezielt für eine Menge unterstellter Modellfehler,

- zufällig ohne Rücksicht auf die interne Struktur und zu erwartende Fehler oder

- Mischformen, z.B. operationprofilorientiert.

Wiederholung einiger Begriffe (Abschn. 2.1.5):

Fehlermodell: Algorithmus, der aus einer simulier- oder abarbeitbaren Beschreibung eine Modellfehlermenge berechnet.

Modellfehler: geringfügige Verhaltens- oder Beschreibungsänderung.

Haftfehler: Annahme von ständig eins oder ständig null für jeden Gatteranschluss

Operationsprofil: Art der Systemnutzung, genauer die relative Nutzungshäufigkeit der Eingaben (Abschn. 3.2.4).

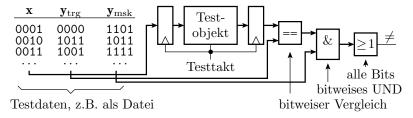

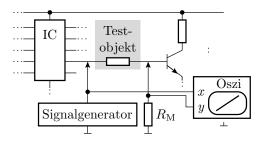

### 6.4 Testausführung für DIC (Abschn. 5.2.2)

Wiederhole üblicherweise für sehr viele Testeingaben:

- zeitgleiche Übergabe der Eingabebits in ein Eingaberegister,

- Ausgabeabtastung mit der nächsten Taktflanke,

- Vergleich mit Sollwerten, opt. Bitausmaskierung.

Probleme: begrenzte Anzahl von Schaltkreisanschlüssen, viele Einund Ausgabesignale, hohe Geschwindigkeit, große Datenmengen, ...

Testeingaben, Testausgaben. x, y

Maskenwerte zum Ausschluss von Testausgaben vom Soll-Ist-Vergleich.  $\mathbf{y}_{\mathrm{msk}}$ Integierter digitaler Schaltkreis (Integrated digital circuit).

Prof. G. Kemnitz · Institut für Informatik, TU Clausthal

DIC

## **DIC-Fehler**

## Fertigungsfehler

### 6.5 Entstehungsprozess, zu erwartende Fehler

#### Schaltkreise entstehen schichtenweise:

- Auftragen von Schichten (z.B. Fotolack oder Metall),

- Belichten des Fotolacks durch eine Maske, die die Geometrie der zu erzeugenden Schichtelemente festlegt,

- Entfernen der belichteten (unbelichteten) Bereiche des Fotolacks.

- Fortätzen der freiliegenden Schichten neben dem Fotolack und entfernen des Fotolacks.

#### Zu erwartende Fehler aus der Fertigung:

- fehlendes (zu wenig aufgetragenes zu viel weggeätztes Material),

- überflüssiges (zu viel aufgetragen, zu wenige weggeätzt Material)

- Maskenversatz, Prozesssteuerfehler, ...

Prof. G. Kemnitz · Institut für Informatik, TU Clausthal

#### 6.6 Globale Fehler und Parameterfehler

#### Globale Fehler:

- Fehlerhafte Schichteigenschaften durch Prozesssteuerfehler. Betroffen sind alle Strukturelemente derselben Schicht (Halbleiter-, Leitungs- oder Isolationsschicht).

- Großflächig überflüssiges oder fehlendes Material. Mehrfachkurzschlüsse oder Unterbrechungen.

Meist erhebliche Funktionsbeeinträchtigung und problemlos zu finden:

- Parametertest (statische Tests): Stichprobenkontrolle der Transistoreigenschaften, Leitwerte und Kapazitäten an den Schaltkreisanschlüssen und speziellen Teststrukturen, auch schon nach Fertigungszwischenschritten.

- Grobtest: Spannung anlegen und kleine Funktionsstichprobe ausprobieren.

Parameter- und Grobtest finden ca. je 1/3 der Schaltkreisfehler und stellen kaum Anforderungen an die Fehlermodellierung und Testsuche.

### 1. DIC-Fehler

### 1. Fertigungsfehler

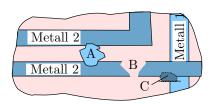

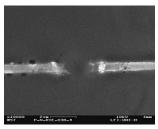

#### 6.7 Lokale Fehler

- A zuätzliches Metall

- fehlendes Metall

- C fehlende Isolation

Einzelfehler durch fehlendes und überflüssiges Material:

- kurzgeschlossene und unterbrochene Verbindungen,

- nicht richtig ein- oder ausschaltende Transistoren bilden sich ab auf ...

#### ... eine große Menge möglicher unterschiedlicher elektrischer Fehlerwirkungen mit

- z.T. sehr geringer Fehlfunktionsrate und Nachweiswahrscheinlichkeit,

- die z.T. logisch nur über verursachte Zusatzverzögerung oder eine erhöhte Ruhestromaufnahme nachweisbar sind.

Fehlermodellierung durch eine für die Testobjektgröße angemessene Anzahl von Modellfehlern.

- die sich mit den tatsächlichen Fehlern Anregungs- und Beobachtungsbedingungen teilen und

- möglichst unabhängig von einander nachweisbar sein sollten (Abschn. 4.3.2).

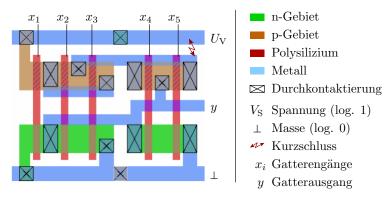

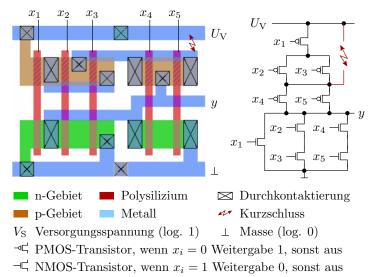

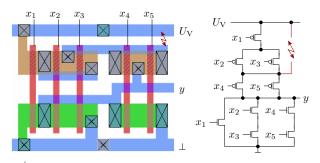

#### 6.9 Geometrie und Funktion

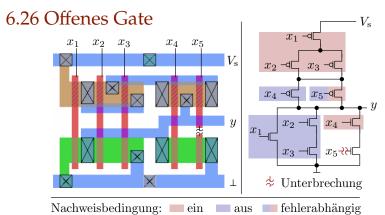

In dem Layoutausschnitt des Logikgatters im Bild ist ein Kurzschluss zwischen zwei benachbarten Leiterbahnen der Metallebene durch nicht weggeätztes Metall unterstellt. Unter welchen Bedingungen verfälscht der Fehler kontrollierbare Ausgaben?

## 6.10 Extraktion der Schaltung

### 6.11 Lokale Fehlernachweisbedingungen

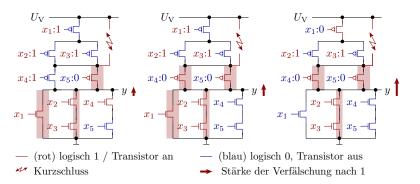

Für den Nachweis muss der Schaltzweig parallel zum Kurzschluss aus und der in Reihe eingeschaltet sein. Die Stärke der Ausgabeverfälschung hängt vom den Leitwerten des Kurzschlusses und der eingeschalteten Transistoren ab. Die Anregung  $x_5x_4x_2x_1 = 00110$  hat die größten Nachweischancen. Statisch nicht »ausreichende« Verfälschungen verzögern den Schaltvorgang und erhöhen den Ruhestrom.

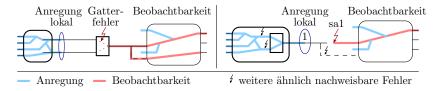

### 6.12 Globale Nachweisbedingungen

Fehlernachweis verlangt außer einer Gattereingabe aus der Fehlernachweismenge (lokale Nachweisbedingung), globale

- Anregungsbedingungen, Schaltungseingaben, die die Gattereingaben steuern und

- Beobachtungsbedingungen, Schaltungseingaben, die vom Gatterausgang einen Beobachtungspfad sensibilisieren.

Die Fehlermodelle, die sich in der Praxis bewährt haben, generieren für jeden zu erwartendenen Fehler mehrere Modellfehler mit denselben globalen Beobachtungsbedingungen und ähnlichen lokalen und globalen Anregungsbedingungen.

### Praxistaugliche Fehlermodelle

#### 6.13 Bewährte DIC-Fehlermodelle

- Haftfehler,

- Gatterverzögerungsfehler und

- Gatterverzögerungsfehler mit Zusatznachweisbedingungen.

Identisch nachweisbare und redundante Modellfehler beseitigen, ... Die Fehlermodelleigenung hängt auch von der Art der Testauswahl ab.

Interessante Ergänzung für CMOS-Schaltkreise: IDDQ-Test, zusätzliche Überwachung der Ruhestromaufnahme nach jedem Testschritt.

Zur Untermauerung der späteren Bewertung der aktuell als ausreichend geltenden Vollständigkeitskriterien für Softwaretests (Abschn. 7.3) werden in einem Folgeabschnitt weitere Testvollständigkeitsmaße für digitale Schaltungen beschrieben, die vor Jahrzehnten genutzt oder als vielversprechend diskutiert wurden und sich nicht bewährt haben.

DIC Integierter digitaler Schaltkreis (Integrated digital circuit).

(F)CMOS Schaltkreise in (vollständig) komplementärer MOS-Schaltungstechnik.

MOS Feldeffektransitoren mit isoliertem Steuer-Gate (MOS – metall oxid semiconductor).

IDDQ Test von CMOS-Schaltkreisen mit Rohestrom-Überwachung.

Prof. G. Kemnitz · Institut für Informatik, TU Clausthal

## 1. DIC-Fehler

### 6.14 Nachweisbeziehung Zufallstests

Eingaberaum

Nachweismenge tatsächlicher Fehlers

Bei (etwa) gleicher Verteilung der Fehlfunktionsrate gleiche zu erwartende Fehlfunktionsüberdeckung für modellierte und tatsächliche Fehler. Eine im Mittel etwas größere oder kleinere Fehlfunktionsrate lässt mit der Testlängenskalierung c herausrechnen (vergl. Abschn. 3.2.3).

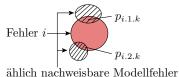

Unser Kurzschlussbespiel hat gezeigt, dass die möglichen Fehlerwirkungen sehr vielfältig sind und sich schwer exakt modellieren lassen. Die ähnlich nachweisbaren Modellfehler je tatsächlicher Fehler haben als gemeinsame Nachweisbedingung »Beobachtbarkeit Gatterausgang« und eine Schnittmenge der lokalen Nachweismengen. Die lokalen Modellfehlernachweismengen sind, wie noch gezeigt wird, je nach Fehlermodell tendentiell größer, gleich oder kleiner als die der Fehler.

## 2. Praxistaugliche Fehlermodelle

### 6.15 Gezielte Testsuche

mit strengen Nachweisbedingungen

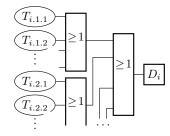

Ein tatsächlicher Fehler i wird nachgewiesen (Ereignis  $D_i$ ), wenn ein gefundener Test für ein ähnlich nachweisbaren Modellfehler j Fehler i nachweist (Ereignis  $T_{ijk}$ , Wahrscheinlichkeit  $p_{ijk}$ ). Eine hohe Erkennungswahrscheinlichkeit  $p_{D,i}$  verlangt vom Fehlermodell

- ähnlich nachweisbare Modellfehler, deren Nachweis mit

- hohe Wahrscheinlichkeiten  $p_{ijk}$  den Fehlernachweis impliziert.

Tendentiell nimmt  $p_{ijk}$  mit der Strenge der Nachweisbedingungen des Fehlermodells zu. Die Nachweibedingungen dürfen aber nur so streng sein, dass der Erfolg der Testsuche nicht beeinträchtigt wird.

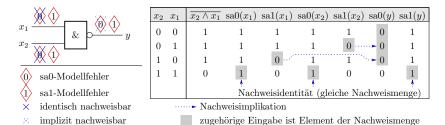

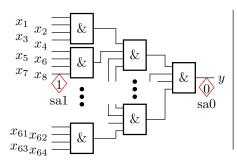

### 6.16 Gatterhaftfehler (Folie 2.26)

#### Für jeden Gatteranschluss wird unterstellt:

- ein sa0 (stuck-at-0) Fehler

- ein sa1 (stuck-at-1) Fehler

#### Nachbearbeitung der Anfangsfehlermenge (bei jedem Fehlermodell):

- Zusammenfassung identisch nachweisbarer Fehler.

- Weglassen von redundanten und optional auch von implizit nachweisbaren Modellfehlern.

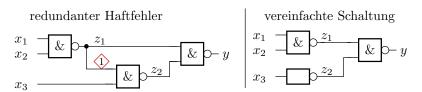

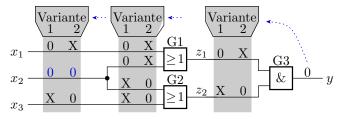

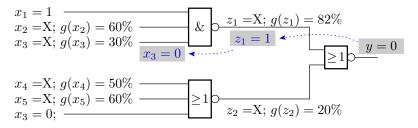

#### 6.17 Redundante Haftfehler (Folie 2.28)

Bei  $z_1 = 0$  ist der Fehler an y nicht beobachtbar und mit  $z_1 = 1$  wird der Fehler nicht angeregt. Nicht nachweisbare Modellfehler sind keine Fehler, aber der Nachweis der »Nichtnachweisbarkeit« ist schwieriger, als für nachweisbare Fehler Tests zu finden.

Redundante nicht als solche erkannte Modellfehler verringern die berechnete Modellfehlerabdeckung und verfälschen darüber die Schätzergebnisse für die tatsächliche Fehlerabdeckung.

Fehlermodelle, die einen hohen Anteil redundanter Fehler generieren, sind sind nicht praxistauglich.

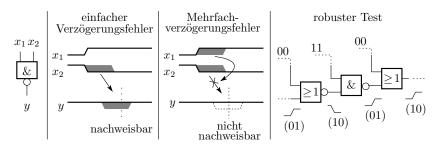

### 6.18 Gatterverzögerungsfehler

- verzögerter Anstieg

- verzögerter Abfall

Fehlernachweis sicher Fehlernachweis möglich kein Fehlernachweis

#### Annahme an allen Gatteranschlüssen

- Slow-To-Raise (verzögerter Signalanstieg) und

- Slow-To-Fall (verzögerter Signalabfall).

Änderung des logischen Werts am Fehlerort als strengere Nachweisbedingung gegenüber Haftfehlern. Längere Zufallstests für gleiche Modellfehlerabdeckung (Nachteil). Vergrößert die  $p_{ijk}$  für Kurzschlüsse und andere zu erwartende tatsächliche Fehler für die gezielte Testsuche (Vorteil).

## 1. DIC-Fehler

#### 6.19 Robuster Nachweis

- Es sind Mehrfachfehler konstruierbar, die sich bei bestimmten Tests gegenseitig maskieren.

- Robuster Nachweis: Ausschluss der gegenseitigen Maskierung durch max. eine Eingabesignaländerung je Gatter und Testschritt.

Strengere Nachweisbedingung als »Gatterverzögerungsfehler«:

- für Zufallstest Nachteil.

- für gezielte Testsuche Vorteil.

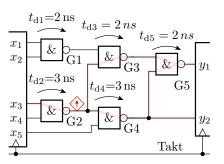

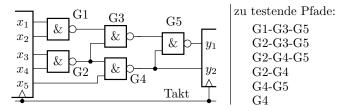

### 6.20 Minimal erkennbare Zusatzverzögerung

| Pfade    | $\sum t_{\mathrm{d.}i}$ |

|----------|-------------------------|

| G1-G3-G5 | 6 ns                    |

| G2-G3-G5 | 7 ns                    |

| G2-G4-G5 | 8 ns                    |

| G2-G4    | 6 ns                    |

| G4-G5    | 5 ns                    |

| G4       | 3 ns                    |

- Die minimal erkennbare Zusatzverzögerung ist die Differenz aus Taktperiode und Soll-Verzögerung.

- Je länger die Sollverzögerung, desto höher die Wahrscheinlichkeit, fehlerverursachte Zusatzverzögerungen zu erkennen.

Test mit  $f_{\rm Clk.max}$  auch für Zufallstest gut. Test über die Pfade mit der max. Sollverzögerung nur für gezielte Testauswahl vorteilhaft.

Prof. G. Kemnitz · Institut für Informatik, TU Clausthal

$t_{d.i}$  Gatterverzögerungszeit.

Schaltungeingabesignale, Schaltungsausgabesignale.

#### **IDDQ-Test**

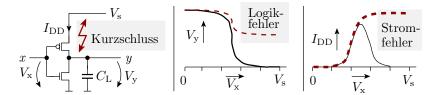

#### 6.21 Ruhestromfehler

In einer CMOS-Schaltung ist der Gatterausgang nur entweder über NMOS-Transistoren mit 0 (Masse) oder über PMOS-Transistoren mit 1 (Versorgungsspannung  $V_{\rm s}$ ) verbunden. Nach jedem Schaltvorgang klingt der Strom auf einen sehr kleinen Wert ab. Kurzschlüsse, nicht richtig ausschaltende Transistoren, ... verursachen, wenn sie Gatterausgaben verfälschen, ein messbar erhöhten Ruhestrom  $I_{\rm DDQ}$ .

| $I_{\mathrm{DDQ}}$      | Versorgungsruhestrom (supply current). Spannung (Potential) von Signal $x$ bzw. $y$ . |  |  |

|-------------------------|---------------------------------------------------------------------------------------|--|--|

| $V_{\rm x}, V_{\rm v}$  |                                                                                       |  |  |

| $V_{\mathrm{s}}, \perp$ | Versorgungsspannung (log. 1), Masse (log. 0)                                          |  |  |

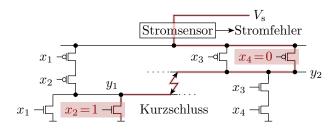

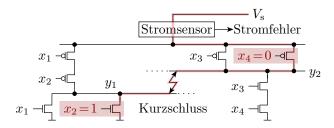

### 6.22 Nachweiseigenschaften

Die Überwachung des Ruhestroms vereinfacht die Nachweisbedingungen für viele FCMOS-typische Fehler erheblich. Nachweisbededingung Kurzschluss im Bild mit IDDQ-Überwachung:  $y_1 \neq y_2$ .

Allgemein genügt die lokale Anregung ohne sensibilisierten Beobachtungspfad zu einem Ausgang:

- Zufallstests: erheblich h\u00f6here effektive Testsatzl\u00e4nge,

- gezielte Testsuche: viel einfachere Testberechnung.

### 6.23 Ruhestrommessung schwierig

Zum erhöhten Ruhestrom des defekten Gatters addieren sich die Ruheströme aller anderen Gatter. Sicheres Erkennen ohne Phantomfehler nur bis zu einigen tausend Gattern. Für größere Schaltungen sind die Stromsensoren der Gattergruppen in die Schaltkreise zu integrieren. Elekrische Probleme, Chip-Fläche für Bypass-Transistoren, ...

Trotzt des hohen Fehlernachweispotentials Einsatz nur für Produkte, die sehr zuverlässig sein müssen und / oder für die geringer Stromverbrauch sehr wichtig ist (Batteriebetrieb).

### Untersuchung einiger Beispielfehler

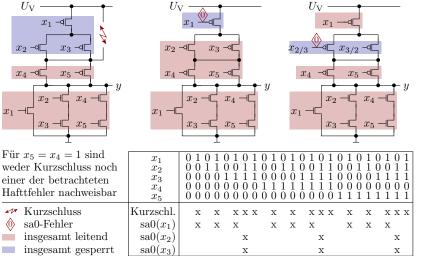

### 6.24 Beispielkurzschluss

- $\neg \Box$  PMOS-Transistor, wenn  $x_i = 0$  Weitergabe 1, sonst aus

- $\dashv \subseteq$  NMOS-Transistor, wenn  $x_i=1$  Weitergabe 0, sonst aus

#### Lokale Nachweisvoraussetzungen:

- PMOS: Netzwerk für  $x_1$  bis  $x_3$  aus, Paralleschaltung  $x_4$  und  $x_5$  an.

- NMOS-Netzwerk: insgesamt an

Ähnlich nachweisbare Haftfehler:  $sa0(x_1)$ ,  $sa0(x_2)$ ,  $sa0(x_3)$ .

Drei (davon zwei identisch nachweisbare) Haftfehler mit kleineren Nachweismengen. Zufallstest und Haftfehler  $c \approx 1 \dots 2$ . Geziele Suche und Gatterverzögerungsfehler  $p_{ijk} < 0.5$ , für Haftfehler geringer.

Der Beispielfehler ist ein abgetrennter Gate-Anschluss. Das isolierte Gate kann auf null oder eins aufgeladen sein und seinen Wert nur sehr langsam ändern. Gleiche lokale Anregungsmenge wie sa0 oder sa1 bzw. slow-to-rise oder slow-to-fall an  $x_5$ . Zufallstest und Haftfehler:  $c \approx 1$ . Geziele Suche mindestens ein Gatterverzögerungsfehler mit  $p_{ijk} = 1$ .

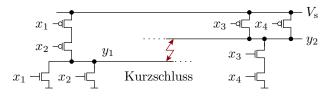

### 6.27 Kurzschluss zweier Gatterausgänge

#### Mögliche Nachweisbedingungen:

$$\bar{\mathbf{x}}_1 \wedge \bar{x}_2 = 1 \text{ und } x_3 \wedge x_4 = 1 \text{ } (y_{1.\mathrm{trg}} = 1 \text{ und } y_{2.\mathrm{trg}} = 0)$$

2

$$x_1 \lor x_2 = 1 \text{ und } \bar{x}_3 \lor \bar{x}_4 = 1 \text{ } (y_{1.\mathrm{trg}} = 0 \text{ und } y_{2\mathrm{trg}} = 1)$$

Ob sich dabei  $y_1 = y_2 = 0$  oder  $y_1 = y_2 = 1$  durchsetzt, hängt von den Transistorbreiten bzw. Transistorsteilheiten ab. Der verfälschte y-Wert muss zusätzlich beobachtbar sein.

Gattereingangssignale, Gatterausgangssignale.  $x_i, y_i$

$V_{\rm s}, \perp$ Versorgungsspannung (log. 1), Masse (log. 0).

#### Ähnlich nachweisbare Haftfehler:

- $sa0(x_1)$ ,  $sa0(x_2)$  wenn  $y_2 = 1$  ist und sich durchsetzt

- $\mathbf{sa1}\left(x_{1}\right),\ \mathbf{sa1}\left(x_{2}\right)$  wenn  $y_{2}=0$  ist und sich durchsetzt

- ullet sa0  $(x_3)$ , sa0  $(x_4)$  wenn  $y_1=1$  ist und sich durchsetzt

- $\bullet$  sa1  $(x_3)$ , sa3  $(x_4)$  wenn  $y_1 = 0$  ist und sich durchsetzt

Zufallstest und Haftfehler: Nachweiswahrscheinlichkeit grob: Wahrscheinlichkeit inverser Pegel auf der anderen Leitung mal Summe der Nachweiswahrscheinlichkeiten von zwei Leitungshaftfehlern,  $c \gtrsim 1$ . Gezielte Auswahl und Haftfehler:  $p_{ijk}$  tendentiell 50%.

$x_i, y_i$  Gattereingangssignale, Gatterausgangssignale.

$V_{\rm s}, \perp$  Versorgungsspannung (log. 1), Masse (log. 0).

c Fehlermodellspezifische Skalierung der effektiven Testanzahl.

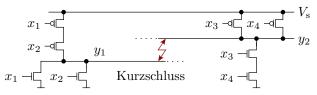

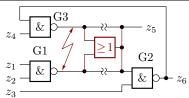

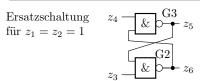

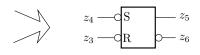

### 6.29 Speicherverhalten durch Kurzschluss

#### Schaltung mit Kurzschluss

#### Kurzschlussnachbildung durch ODER

| $z_4 z_3 z_2 z_1$ | $z_6 z_5$     |

|-------------------|---------------|

| 0 1 1 1           | 0 1 (setzen)  |

| 1 0 1 1           | 1 0 (löschen) |

| 1 1 1 1           | speichern     |

| $z_4 z_3 z_2 z_1$ | $z_6 z_5$     |

|-------------------|---------------|

| 0 0 1 1           | 1 1           |

| 1                 | ↓ ändern nach |

| 1 1 1 1           | unbestimmt    |

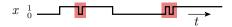

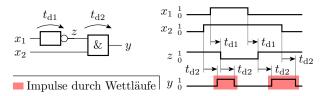

### 6.30 RS-Flipflops, Glitches und Wettläufe

Glitches sind kurze Pulse, die bei logischen Verknüpfungen von Signalen mit unterschiedlicher Verzögerung entstehen, die unser RS-Flipflop für  $x_4x_3x_2x_1 = 0011$  setzen oder rücksetzen können.

Ursache Wettläufe und rekonvergente Signalflüsse. Wettläufe sind fast zeitgleiche Änderungen an mehreren Eingängen einer vorgelagerten Teilschaltung. Auch wenn vor und nach der Änderung derselbe Wert ausgegeben wird, treten im Änderungsmoment kurze Pulse auf.

### 6.31 Fehlerwirkung vs. Modellierung

Die wenigen Beispiele haben gezeigt, dass die Wirkungen einzelnen Kurzschlüsse und Unterbrechungen sehr vielfältig und kaum exakt zu modellieren ist, weil auch von Laufzeiten, Leitwerten und der Fehlerausprägung abhängig. Nicht betrachtet aber auch möglich sind Abhängigkeiten von der Versorgungsspannung, der Temperatur, ...

Je exakter ein Fehlermodell die möglichen tatsächlichen Fehlerwirkungen annähert, desto mehr sehr ähnlich nachweisbare Modellfehler. Zumindest für Zufallstest nicht zielführend. Bei gezielter Testsuche beeinträchtigen zu komplizierte Nachweisbedingungen den Sucherfolg.

Etabliert haben sich statt dessen die am einfachsten zu modellierenden lokalen logischen Fehlerannahmen:

- Haftfehler und

- Haftfehler mit Zusatzbedingungen.

Für einen Zufallstest deuten die Beispiele auf fehlermodellspezifische Skalierung der effektiven Testanzahl von mindesten c > 1.

- Ohne redundante Modellfehler ist die zu erwartende Fehlerüberdeckung nicht schlechter als die Modellfehlerüberdeckung.

- Eine ausreichende Testanzahl für Modellfehler ist auch ausreichend für tatsächliche Fehler.

Für gezielte Testauswahl sind die Haftfehler-Zusatzbedingungen zur Erhöhung von  $p_{ijk}$  empfehlenswert:

- Signalwechsel am Fehlerort (Gatterverzögerungsfehler),

- robuster Nachweis und

- Nachweis über den Pfad mit der längst Soll-Verzögerung.

Alle drei Zusatzbedingungen haben den Vorteil, dass sie sich auf die Eingaben vor dem Haftfehlernachweis beziehen, und damit die Testsuche für den Haftfehlernachweis nicht erschweren.

Auch bei strengem Fehlermodell Suche mehrerer zufällig ausgewählten Tests aus der Nachweismenge von jedem Modellfehler zweckmäßig.

### 6.33 Modellfehler- und Defektabdeckung DIC

In der Beispielrechnung 3.2 wurde abgeschätzt, dass Schaltkreistests bei den typischen Schaltkreisausbeuten von  $Y \approx 30\% \dots 90\%$ Defektabdeckungen von  $DC \approx 99.9\%$  haben müssten, um auf die in der Literatur zu findenden Defektanteile von  $DL = 200 \,\mathrm{dpm}$  bis  $1.000\,\mathrm{dpm}$  zu kommen.

Schaltkreistests habe Haftfehlerabdeckungen in der Größenordnung  $FC_{\rm M} = 95\% \dots 99\%$ . Der Anteil der nicht nachweisbaren defekten Schaltkreise müsste mindestens eine Zehnerpotenz kleiner als der Anteil der nicht nachweisbaren Haftfehler sein.

#### Ist das glaubwürdig?

| Y           | Ausbeute (Yield).                                                          |

|-------------|----------------------------------------------------------------------------|

| DL          | Defektanteil nach Aussortieren oder Ersatz erkannter defekter Produkte.    |

| DC          | Defektabdeckung (defect coverage), Anteil der erkennbar defekten Produkte. |

| $FC_{ m M}$ | Modellfehlerabdeckung.                                                     |

- Typ. 2/3 der Schaltkreisdefekte sind globale Fehler, die von den Parameter- und Grobtests zu 100% nachgewiesen werden. Verringerung der Lücke bis um Faktor 3.

- Die zu erwartende Defektabdeckung ist die Wahrscheinlichkeit, das mindestens ein Fehler erkannt wird. Bei Ausbeuten  $Y \approx 30\% \dots 90\%$  sind Mehrfachfehler typisch. Clusterung erhöht die den Anteil der Schaltkreise mit Mehrfachfehlern. Mehrfachfehler sind einfacher zu erkennen als Einzelhaftfehler.

- Auch Kurzschlüsse Kurzschlüsse und Unterbrechungen tendentiell dazu, einfacher als Haftfehler nachweisbar zu sein.

- Die Angaben zur Haftfehlerüberdeckung werden durch nicht erkannte redundante Haftfehler verfälscht.

Ein Anteil der nicht nachweisbaren Defekte von weniger als einem Zehntel des Anteils der nicht nachweisbaren Modellfehler ist denkbar, aber eine höher Dunkelziffer des Defektanteils aufgelieferter Schaltkreise ist auch möglich. Forschungsbedarf!

### Veraltetet Testvollständigkeitsmaße

### 6.35 Veraltetet Testvollständigkeitsmaße

Nicht alle Fehlermodelle und Testvollständigkeitsmaß, die vor Jahrzehnten für digitale Schaltungen genutzt oder als vielversprechend diskutiert wurden, haben sich bewährt.

Software hat gegenüber Hardware die Vorzüge; einfache Änderbarkeit und große funktionale Redundanz. Wenn die Anwender Probleme bemerken, stellten sie ein Change-Request oder suchen ein Workaround. Das hat die Forschung zum Testen gegenüber Hardware um Jahrzehnte zurückgestellt.

Die heute für den Softwaretests als ausreichend geltenen Testvollständigkeitsmaße (Abschn. 7.3):

- alle Anweisungen ausprobieren (Anweisungsüberdeckung),

- alle Zweige ausprobieren (Zweigüberdeckung), ...

gabe es vor Jahrzehnten in ähnlicher Form für Hardware.

Vor diesem Hintergrund lohnt ein Blick, was sich für digitale Schaltungen alles nicht bewährt hat und in Vergessenheit geraten ist.

### 1. DIC-Fehler 5. Veraltetet Testvollständigkeitsmaße

### 6.36 Toggle-Test

Vor der Zeit der fehlermodellbasierten Testauswahl und -bewertung diente die Toggle-Abdeckung als Testvollständigkeitsmaß:

```

für alle Leitungen

0 einstellbar,

1 einstellbar.

```

Unberücksichtigte Nachweisbedingungen:

- Beobachtbarkeit lokaler Verfälschungen,

- paarweise unterschiedlicher Werte für Kurzschlussnachweis, ...

Eine 0 oder 1 am Fehlerort impliziert nur mit geringer Wahrscheinlichkeit einen Fehlernachweis. Wenn alle Nullen und Einsen gleich gut beobachtbar, Testlängenskalierung c gleich Beobachtbarkeit, aber ...

100%-Toggle-Überdeckung erlaubt kaum Rückschlüsse auf die Fehlerüberdeckung.

### 1. DIC-Fehler 5. Veraltetet Testvollständigkeitsmaße

### 6.37 Pfadverzögerungsfehler

Fehlerannahme »Slow-To-Rise« / »Slow-To-Fall« für alle Signalpfade. Die Beispielschaltung hat fünf Gatter und 6 Signalpfade. 100% Pfadfehlerabdeckung schließt die Tests über die Pfade mit der längsten Solllaufzeit immer mit ein. Als Fehlermodell ungeeignet weil:

- Im ungünstigen Fall exponentielle Zunahme der Pfadanzahl mit der Gatteranzahl. Große Nachweisähnlichkeiten, großes  $\kappa$  ...

- Nicht über alle Pfade lassen sich Signalwechsel propagieren. Viel redundante Fehler.

# 1. DIC-Fehler 5. Veraltetet Testvollständigkeitsmaße

### 6.38 Zellenfehler

Idee: Definition von Bausteintestsätzen, die durch die umgebende Schaltung gesteuert und beobachtbar gemacht werden müssen. Jeder Bausteintest wird als Modellfehler gezählt.

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$ | Sc               | oll-Fu | Soll-Funktion            | 7   | Zeller | fehle | r   |

|--------------------------------------------------------|------------------|--------|--------------------------|-----|--------|-------|-----|

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$  | $\overline{x_1}$ | $x_0$  | $x_1  x_0  x_1 \lor x_0$ | F00 | F01    | F10   | F11 |

|                                                        | 0                | 0      | 0 0                      | 1   | 0      | 0     | 0   |

|                                                        | 0                | 1      | ) 1   1                  | 1   | 0      | 1     | 1   |

|                                                        | 1                | 0      | 1 0   1                  | 1   | 1      | 0     | 1   |

| $egin{array}{ c c c c c c c c c c c c c c c c c c c$   | 1                | 1      | 1 1 1                    | 1   | 1      | 1     | 0   |

Für ein Gatter könnte der lokalen Tests der mit allen Eingaben sein. Im Beispiel  $2^2 = 4$  Zellenfehler statt 6 initiale Haftfehler. Als Fehlermodell meist nicht geeignet weil:

- Beim Test der Zellen mit allen Eingabemöglichkeiten exponentielle Zunahme der Modellfehleranzahl mit der Anzahl der Gattereingänge und viele ähnlich nachweisbare Modellfehler.

- Viel der lokalen Tests nicht durch die umgebende Schaltung steuerund beobachtbar. Viele redundante Fehler.

# 6.39 C-Test

Bewährt hat sich die Idee des Zellenfehlermodells für die Konstruktion von sog. C-testbaren regelmäßig strukturierten Schaltungen, Speicher, Addierer, Multiplizierer, ...

Dabei werden die Zellenfunktion, der Zellentestsatz und die Schaltungsstruktur so aufeinander abgestimmt entwickelt, dass sich ein Testsatz mit 100% Zellenfehlerüberdeckung (ein C-Test) generieren lässt (sie später Abschn. 6.2.7).

## Zusammenfassung

### 6.40 Global und lokale Fehler, Testauswahl

- Schaltkreise entstehen schichtenweise. Globale Fehler sind großflächig, leicht nachweisbar und für die Testauswahl uninteressant.

- Lokale Fehler unterbrechen oder verbinden einzelne Schichtelemente, modellierbar als fehlendes oder zusätzliches Material.

- Kurzschlüsse und Unterbrechungen von Schichtelementen bilden sich auf Kurzschlüsse und Unterbrechungen von Verbindungen und nicht richtig bzw. zu langsam schaltende Transistoren ab.

- Die elektrische und logische lokale Wirkung und Nachweisbarkeit ist vielfältig und oft nicht exakt vorhersagbar.

- Modellfehler teilen sich mit den tatsächlichen lokalen Fehlern Anregungsbedingungen und die Beobachtbarkeit des Gatterausgang.

- Für Zufallstest genügene Modellfehler mit ähnlich großen lokalen Nachweismengen.

- Für gezielte Testauswahl ist es wichtiger, dass Tests für ähnlich nachweisbaren Modellfehler mit großer Wahrscheinlichkeit  $p_{ijk}$  tatsächliche Fehler nachweisen.

### 6.41 Bewährte Fehlermodelle

Für Zufallstest ist das Haftfehlermodell Favorit. Die untersuchten Beispiele deuten auf eine fehlermodellspezifische Skalierung der effektiven Testanzahl von mindesten c > 1.

- Ohne redundante Modellfehler ist die zu erwartende Fehlerüberdeckung nicht schlechter als die Haftfehlerüberdeckung.

- Eine ausreichende Testanzahl für Haftfehler ist auch ausreichend für tatsächliche Fehler.

Für gezielte Testauswahl sind Zusatzbedingungen zur Verbesserung der  $p_{ijk}$  zielführend:

- Signalwechsel am Fehlerort (Gatterverzögerungsfehler),

- robuster Nachweis und

- Nachweis über den Pfad mit der längst Soll-Verzögerung.

- Statt oder in Ergänzung der Zusatzbedingungen, zufällige Auswahl mehrerer Tests aus der Nachweismenge von jedem Modellfehler.

### 6.42 Sonstiges

IDDQ-Test: Beobachtung von Fehlern am erhöhten Ruhestrom nach Schaltvorgängen. Erhöht die effektive Testanzahl und vereinfacht Testsuche erheblich. IDDQ-Überwachung aber so problematisch, das Einsatz nur bei sehr hohen Anforderungen an die Verlässlichkeit und Batterielaufzeit.

Anteil der nicht nachweisbaren defekten Schaltkreise um einen Faktor zehn kleiner als Anteil der nicht nachweisbaren Modellfehler? Denkbar, aber genauere Untersuchen wünschenswert.

Ein ähnliches Testvollständigkeitsmaß wie heute die Anweisungsüberdeckung für Software gab es früher auch für Hardware, den Toggle Test. Heute in Vergessenheit geraten.

# Testsuche

# 2. Testsuche

211

$w_i$

### 6.43 Testauswahl, gezielte Suche

#### Beginn mit zufälliger Auswahl:

Wiederhole, solang Nachweis von genug neuen Fehler je Test

Fehlersimulation mit neuen Zufallseingaben und Inkrement der Nachweisanzahl  $w_i$  für alle nachweisbaren Modellfehler i

#### Dann Umschaltung auf gezielte Testsuche:

Wiederhole für alle Modellfehler i:

Suche w Tests oder Redundanznachweis Abbruch bei Überscheitung einer gesetzten Rechenzeitgrenze

Problematisch sind redundante Fehler, genauer der Nachweis, dass es für einen Modellfehler keine Nachweismöglichkeit gibt und er folglich nicht als Modellfehler zählt.

> Anzahl der ie Modellfehler gesuchten Tests. Gefunden werden alle oder keiner. Anzahl der für Modellfehler i gefundenen Tests.

### Fehlersimulation

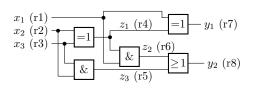

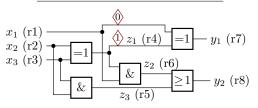

### 6.44 Logiksimulation digitaler Schaltungen

#### Schaltung eines Volladdierers

r1 bis r8 Prozessorregister

#### Programm für die Gutsimulation

- 1 lade  $x_1$  in Register r1

- 2 lade  $x_2$  in Register r2

- 3 lade  $x_3$  in Register r3

- 4 r4 = r2 xor r3

- 5 speichere Inhalt r4 in  $z_1$

- 6 r5 = r2 and r3

- 7 speichere Inhalt r5 in  $z_3$

- 8 r6 = r1 and r4

- 9 speichere Inhalt r6 in  $z_2$

- 10 r7 = r1 xor r4

- 11 speichere Inhalt r7 in  $y_1$

- 12 r8 = r5 or r6

- 13 speichere Inhalt r8 in  $y_2$

- Jede zweistellige Logikoperation ist ein Maschinenbefehl.

- In jeder der 32 oder 64 Bits der Operanden kann ein anderer Testfall oder ein anderer Fehler simuliert werden.

- Mit 64-Bit-Prozessor ca. 16 simulierte Gatterfkt. / Prozessortakt.

### 6.45 Haftfehler und Zusatzbedingungen

#### Fehlerparallele Haftfehlerimulation

```

9 ...

; sa0(x_1) in Bit 0

r8 = r1 and ...1110

; sa1(z_1) in Bit 1

r9 = r1 or ...0010

10 r7 = r8 xor r9

11 speichere Inhalt r7 in y_1

```

- Haftfehler werden durch setzen bzw. Löschen von Bits durch UND/ODER mit Bitvektorkonstanten simuliert.

- Zusatzbedingungen wie Signalwechsel am Fehlerort, wenn Haftfehler nachweisbar (Gatterverzögerungsfehler), sind Logikbeziehungen zu Bitergebnissen der Simulation für Testschritt davor, modellierbar durch wenige zusätzlichen Lade- und Logikbefehle.

Haftfehler und Zusatzbedingungen sind bitparallel mit wenigen Prozessorbefehlen simulierbar.

### 6.46 Aufwandsabschätzung am Beispiel

- Schaltungsgröße: 10<sup>4</sup> Gatter

- Anzahl der Testschritte / Testeingaben: 10<sup>4</sup>

- Anzahl der Modellfehler: 10<sup>4</sup>

- Simulationsaufwand je Gatter: 10 ns

#### Rechenaufwand:

- Wenn jeder Fehler mit allen Testeingaben simuliert wird und ohne bitparallele Simulation: 10<sup>4</sup> s, ca. 3 h.

- Wenn mit jedem der 32 bzw. 64 Bits ein anderer Fehler simuliert wird, nur 6 bzw. 3 Minuten.

- Wenn bereits ausreichend oft nachgewiesene Modellfehler nicht weiter mit simuliert werden, unter 1 Minute.

Erheblicher Rechenaufwand entfällt auf die nicht erkannten redundanten Modellfehler.

In  $10 \, \mathrm{s}$  Testzeit können bei einer Taktfrequenz von 100 MHz bis zu  $10^9$ Tests ausgeführt werden. Eine Fehlersimulation von  $10^9$  Test dauert auch bitparallel auf einem Prozessor viele Tage.

### **D-Algorithmus**

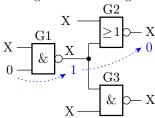

### 6.47 D (Discrepancy)-Kalkül von Roth

Erweiterung der Logikwerte um 3 Pseudo-Werte [Deahn97]:

- X Signalwert nicht festgelegt oder beliebig

- D 0 wenn unverfälscht, 1 wenn verfälscht.

- D 1 wenn unverfälscht, 0 wenn verfälscht.

Regeln für die Sensibilisierung eines Beobachtungspfades:

D Discrepanz-Kalkül, 0 wenn unverfälscht, 1 wenn verfälscht.

X Signalwert ungültig oder für den Fehlernachweis ohne Bedeutung.

[Daehn97] Testverfahren in der Mikroelektronik: Methoden und Werkzeuge. Springer 1997.

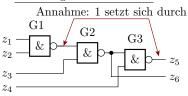

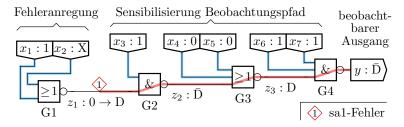

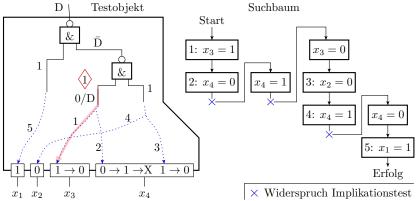

#### 6.48 Testsuche für Haftfehler

Ein Haftfehler unterstellt für den Fehlerort, dass der Wert

- entweder ständig 0 (sa0) oder

- ständig 1 ist (sa1) ist.

Ausgehend vom Fehlerort werden Eingaben gesucht,

- für die der Wert am Fehlerort invertiert wird und

- bei denen die Invertierung am Fehlerort an einem Ausgang beobachtbar ist.

Eingabe-, Ausgabe- und interne Signale.  $x_i, y_i, z_i$ Discrepanz-Kalkül. 0 wenn unverfälscht. 1 wenn verfälscht.

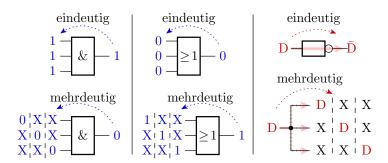

### 6.49 Ein- und mehrdeutige Pfade

#### Ausgehend vom Fehlerort:

- Wertefestlegung zur Weiterführung von Beobachtungs- oder Steuerpfaden.

- Für nicht eindeutige Festlegungen sind Entscheidungen zu treffen.

- Bei Widersprüchen Änderung der letzten Entscheidung mit einer noch nicht untersuchten Alternative (Baumsuche).

- Widerspruch und keine Alternative ⇒ Modellfehler redundant.

G3

G2

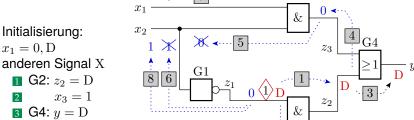

### 6.50 Testsuche für einen einzelnen Fehler

- - $z_3 = 0$

- G3:  $x_2 = 0$

- G1:  $x_2 = 1 \neq 0$  (Wiederspruch)

- G3 Neue Entscheidung:  $x_1 = 0$

- G1:  $x_2 = 1$

Wiederhole bis Test gefunden oder Redundanz nachgewiesen:

- Vervollständige Anschlusssignals eines Gatters, ...

- Wenn Widerspruch, Änderung letzte freie Entscheidung.

### 6.51 Zusatzbedingungen

Die Zusatzbedingungen »Gatterverzögerungsfehler«, »robuster Nachweis« und »Pfad mit längster Sollverzögerung« beschreiben Logikbedingungen für die Testeingaben davor.

Für den sa1-Fehler im Beispiel ist für den Zeitschritt davor eine eins am Fehlerort einzustellen.

Suche geeigneter Testeingaben dafür in der Regel viel einfacher als für den Haftfehler, weil kein Beobachtungspfad sensibilisiert werden muss.

### 6.52 Optimierung Suchalgorithmus

- Die Testsuche f

ür einen Fehler kann hunderte von Wertefestlegungen beinhalten.

- Der Suchraum wächst exponentiell mit der Anzahl der mehrdeutigen Festlegungen. Suchräume der Größen  $> 2^{30...40}$ nicht mehr vollständig durchsuchbar.

- Abbruch der Suche nach einer vorgegebenen Zeitschranke.

#### Erfolgsrate der Testberechnung:

Anteil der Fehler, für die ein Test gefunden oder für die der Beweis »nicht nachweisbar« erbracht wird.

#### Heuristiken zur Verbesseerung der Erfolgsrate:

- Frühe Erkennung von Widersprüchen (Äste im Suchbaum abschneiden),

- Suchraumbegrenzung und

- qute Suchraumstrukturierung.

## Implikationstest

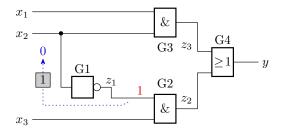

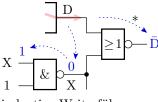

### 6.54 Implikationstest

...zur frühzeitigen Erkennung von Widersprüchen:

Nach jeder Wertefestlegung alle eindeutig folgenden Werte festlegen.

Implikation in Signalflussrichtung

D-Pfad- und Rückwärtsimplikation

\* eindeutige Weiterführung

■ Im Beispiel (Folie 6.50) sind alle Werte eindeutig.

Discrepanz-Kalkül, 0 wenn unverfälscht, 1 wenn verfälscht.

Signalwert ungültig oder für den Fehlernachweis ohne Bedeutung.

Rückwärtsimplikation über mehrere Gatterebenen:

- lacksquare Für y=0 gibt es zwei Einstellmöglichkeiten.

- Für beide Möglichkeiten muss  $x_2 = 0$  sein.

- Das Erkennen von Implikationen dieser Art mindert die Backtracking-Häufigkeit um bis zu 80 %.

$x_i,\,y_i,\,z_i$  Eingabe-, Ausgabe- und interne Signale. X Signalwert ungültig oder für den Fehlernachweis ohne Bedeutung.

### Suchraumstrukturierung

### 6.56 Suchraumbegrenzung

- Der D-Algorithmus baut den Suchbaum über alle mehrdeutigen Wertefestlegungen auf.

- Nur die Schaltungseingänge k\u00f6nnen unabh\u00e4ngig voneinander alle Wertekombinationen annehmen.

- Es genügt, den Suchbaum mit den Eingabewertefestlegungen aufzubauen.

- Begrenzt Suchraum auf  $2^{\#x}$ . Verringert Rechenaufwand um Zehnerpotenzen.

#x Anzahl der Schaltungseingänge.

Χ

- Lange Steuerpfade vom Fehlerort und vom D-Pfad zu Eingängen.

- Aufbau des Suchbaums über Eingangssignale.

- Wenn Implikationstest-Widerspruch, letzte Eingabefestlegung invertieren.

Signalwert ungültig oder für den Fehlernachweis ohne Bedeutung. Discrepanz-Kalkül, 0 wenn unverfälscht, 1 wenn verfälscht.

### 6.58 Geschätzte Erfolgswahrscheinlichkeiten

- Schätzen der Signalwichtungen  $g(x_i)$  über eine kurze Simulation mit Zufallswerten oder analytisch.

- Wahl der Steuerwerte / Beobachtungspfade, die mit größerer Wahrscheinlichkeit aktivierbar / sensibilisierbar sind.

```

Eingabe-, Ausgabe- und interne Signale.

x_i, y_i, z_i

Signalwert ungültig oder für den Fehlernachweis ohne Bedeutung.

g(\ldots)

Wichtung, Auftrittshäufigkeit des Signalwerts 1.

```

### Komplexe Funktionsbausteine

### 6.59 Komplexe Funktionsbausteine

Beschreibung durch Tabellenfunktion (Bsp. Volladdierer):

| $x_2$ | $x_1$ | $x_0$ | s | c | gegeben Lösungsmenge                                                                   |

|-------|-------|-------|---|---|----------------------------------------------------------------------------------------|

| 0     | 0     | 0     | 0 | 0 | $XXX00 \Rightarrow 00000 \text{ (eindeutig)}$                                          |

| 0     | 0     | 1     | 1 | 0 |                                                                                        |

| 0     | 1     | 0     | 1 | 0 | $ \begin{cases} 01DXX \Rightarrow 01D\overline{D}D \text{ (eindeutig)} \end{cases} $   |

| 0     | 1     | 1     | 0 | 1 | ordan → ordan (emdeurig)                                                               |

| 1     | 0     | 0     | 1 | 0 |                                                                                        |

| 1     | 0     | 1     | 0 | 1 | $1XXXD \Rightarrow 10D\bar{D}D, 1D0\bar{D}D (2 Alternativen)$                          |

| 1     | 1     | 0     | 0 | 1 | $11XX1 \Rightarrow 11111, 11001 (2 Alternativen)$                                      |

| 1     | 1     | 1     | 1 | 1 | $\begin{cases} 111111 & \Rightarrow 11111, 11001 \text{ (2 Alternativen)} \end{cases}$ |

- Vervollständigung des Vektors der gegebenen Anschlusswerte durch Vergleich mit allen Tabellenzeilen:

- »1« und »0« passen nur auf »1« und »0«.

- »X« passt immer.

- »D« muss für eine Zeile mit »D=0« und eine Zeile mit »D=1« passen.

- Discrepanz-Kalkül, 0 wenn unverfälscht, 1 wenn verfälscht. Signalwert ungültig oder für den Fehlernachweis ohne Bedeutung.

D

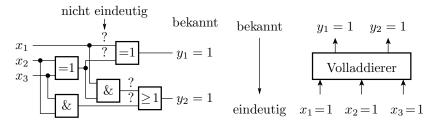

### 6.60 Implikationstest an einem Volladdierer

- An der Gatterbeschreibung eines Volladdierers ist die Implikation  $y_1 = y_2 = 1 \Rightarrow x_1 = x_2 = x_3 = 1$  nicht zu erkennen. Lösungsfindung über Baumsuche.

- Bei Zusammenfassung zu einer Tabellenfunktion wird die Lösung bereits bei der Anschlusswertevervollständigung erkannt.

## 2. Testsuche 5. Komplexe Funktionsbausteine

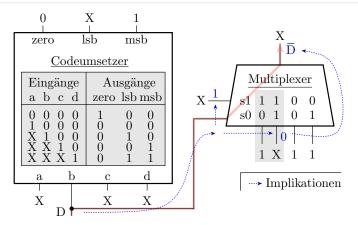

- »Isb« hängt bei »zero=0« und »msb=1« nicht von »b« ab. Nur über den Multiplexer lässt sich der D-Pfad weiterführen, ...

- lacktriangle Tabelleneingabewerte »X« führt zu Tabellen mit  $\ll 2^w$  Zeilen.

$\begin{array}{ll} {\rm D} & {\rm Discrepanz\text{-}Kalk\"ul,\,0\ wenn\ unverf\"alscht,\,1\ wenn\ verf\"alscht.} \\ {\rm X} & {\rm Signalwert\ ung\"ultig\ oder\ f\"ur\ den\ Fehlernachweis\ ohne\ Bedeutung.} \\ w & {\rm Anzahl\ der\ Eingabebits.} \end{array}$

## Sequentielle Schaltungen

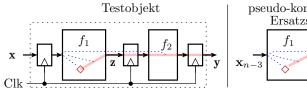

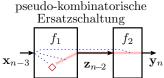

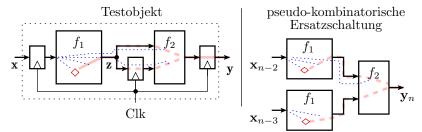

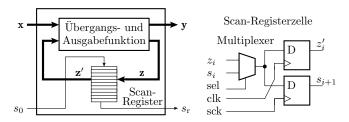

## 6.62 Pseudo-kombinatorische Ersatzschaltung

Schaltungen mit Speicherelementen werden für die Testsuche zu einer pseudo-kombinatorischen Ersatzschaltung aufgerollt. Abtastregister in einem geradlinigen Berechnungsfluss werden weggelassen:

- Testberechnung wie für eine kombinatorische Schaltung.

- Die Verzögerungen der Ausgabe gegenüber der Eingabe wird erst beim Zusammensetzen der Testeingaben und Sollausgaben berücksichtigt.

x, y, zClk

Bitvektor der Eingabe-, Ausgabe- und internen Signale, Index ist Zeitschrittnummer. Taktsignal (Clock signal).

## 6.63 Verarbeitung in mehreren Zeitebenen

- Mehrere Kopien gleicher Schaltungsteile in der pseudo-kombinatorischen Ersatzschaltung.

- Der eingebaute Haftfehler ist in jeder Kopie der Teilschaltung.

- Für jeden Fehler wird eine Folge von Testeingaben für mehrere Zeitschritte berechnet (Mehr-Pattern-Test).

- Erschwert die Einstellung der Zusatzbedingungen in den Zeitschritten zuvor.

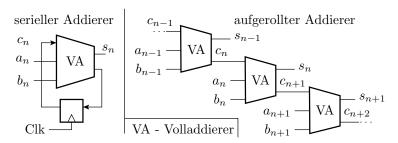

## 6.64 Schaltungen mit Rückführung

- Pseudo-kombinatorischen Ersatzschaltung mit endlos vielen Kopien der Übergangsfunktion.

- Längenbegrenzung der Steuer- und Beobachtungspfade.

- Alternative: Scan-Zugriff auf Übertragsbit (Folie 5.37).

```

\begin{array}{lll} a_i,\,b_i & \text{Summandenbit } i. \\ s_i & \text{Summenbit } i. \\ c_i & \text{Übertragsbit } i. \\ \text{Clk} & \text{Taktsignal (Clock signal)}. \end{array}

```

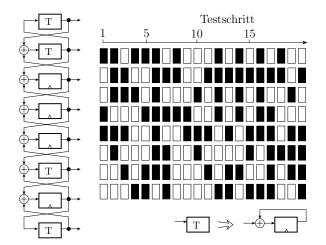

## 6.65 Scan-Verfahren (Folie 5.37)

Lese- und Schreibzugriff während des Tests durch Umschalten des Zustandsspeicher in ein r-Bit Schieberegister.

- Alternierend r Schiebeschritte zum Beschreiben und Lesen des Scan-Registers und eine Testschritt.

- Optional getrennte Register f

ür Schieben und Daten f

ür Zusatzbedingung »Gatterverzögerungsfehler.

Bitvektor der Eingabe- und Ausgabesignale. x, y

Bitvektor der Zustands- und der abgetasteten Zustandssignale.

Serielles Schiebesignal i, Umschaltsignal zwischen Schiebe- und Normalmodus.  $s_i$ , sel clk, sck

z, z'

## Speichertest

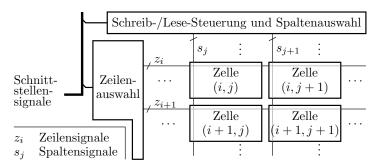

## 6.66 Blockspeicher

Große Speicher besteht im Kern aus einer regelmäßigen 2D-Anordnung von flächenminimierten Speicherzellen umgeben von der Zeilen- und Spaltenauswahlschaltung. Die Grundfunktionen (nur lesbar, beschreibund lesbar, ...) hängen von der Zellenfunktion ab.

Testauswahl: Festlegen der Test für eine Zelle. Konstruktion eine Gesamttestablaufs, der alle Zellentests enthält (C-Test, Folie 6.39).

#### 6.67 Zellenfehler für RAM

| beteiligte<br>Zellen | Name                                                                                        | Definition                                                               | Fälle                                                                                                                                                | Testfolge für den<br>Nachweis                                                                                              |

|----------------------|---------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

|                      |                                                                                             |                                                                          | stuck-at-0<br>stuck-at-1                                                                                                                             | $W(i)1, R(i)1 \ W(i)0, R(i)0$                                                                                              |

| 1                    | Übergangs-<br>fehler                                                                        | Wert der Speicherzelle $i$ ist nur in einer Richtung änderbar            | $\begin{array}{c} \text{kein } \ddot{\text{U}} \text{bergang} \\ 1 \rightarrow 0 \\ 0 \rightarrow 1 \end{array}$                                     | $W(i)1, R(i)1, W(i)0, R(i)0 \ W(i)0, R(i)0, W(i)1, R(i)1$                                                                  |

|                      | Stuck-open-<br>Fehler cherzelle i (Ausgabe<br>des Wertes der vorhe-<br>rigen Lescoperation) |                                                                          |                                                                                                                                                      | $W(i)0, R_1(j), R(i)0, W(i)1,$<br>$R_0(j), R(i)1$                                                                          |

|                      | zerstören-<br>des Lesen                                                                     | Inhalt von Speicherzelle i wird beim<br>Lesen verändert                  | $R(i) \Rightarrow C(i) = \overline{C(i)}$                                                                                                            | W(i)0, R(i)0, R(i)0<br>W(i)1, R(i)1, R(i)1                                                                                 |

| 2                    | Kopplung<br>Typ 1                                                                           | Veränderung des Inhalts von Zelle $i$ bestimmt Zustand in Zelle $j$      | $\begin{split} W(i)0 &\Rightarrow C(j) = 0 \\ W(i)0 &\Rightarrow C(j) = 1 \\ W(i)1 &\Rightarrow C(j) = 0 \\ W(i)1 &\Rightarrow C(j) = 1 \end{split}$ | $\begin{array}{c} W(j)0,W(i)0,R(j)0,\\ W(i)1,R(j)0\\ W(j)1,W(i)0,R(j)1,\\ W(i)1,R(j)1 \end{array}$                         |

|                      | Kopplung<br>Typ 2                                                                           | Veränderung des Inhalts von Zelle $i$ bewirkt eine Änderung in Zelle $j$ | $C(i) = \overline{C(i)} \Rightarrow C(j) = \overline{C(j)}$                                                                                          | $\begin{array}{c} W(j)0,W(i)0,R(j)0,W(i)1,\\ R(j)0,W(i)0,R(j)0\\ W(j)1,W(i)0,R(j)1,W(i)1,\\ R(j)1,W(i)0,R(j)1 \end{array}$ |

W(i)0 Schreibe in Zelle i eine 0

W(i)1 Schreibe in Zelle i eine 1 R(j)Lese eine beliebige andere Zelle

$C(\ldots)$  Inhalt Zelle  $\ldots$

R(i)0 Lese Inhalt Zelle i und vergleiche mit Sollwert 0

R(i)1 Lese Inhalt Zelle i und vergleiche mit Sollwert 1

$R_0(i)$  Lese eine andere Zelle, in der 0 steht  $R_1(i)$  Lese eine andere Zelle, in der 1 steht

## 6.68 Marching Test

| $\mathop{\mathrm{Adresse}}_{i}$                             | Initiali-<br>sierung                                                      | March 1 |           |             | March :                                                                                                        | 2          | March 3                                                                  |  |  |

|-------------------------------------------------------------|---------------------------------------------------------------------------|---------|-----------|-------------|----------------------------------------------------------------------------------------------------------------|------------|--------------------------------------------------------------------------|--|--|

| $\begin{array}{c} 0 \\ 1 \\ 2 \\ \vdots \\ N-1 \end{array}$ | $\begin{array}{c} W(i)0 \\ W(i)0 \\ W(i)0 \\ \vdots \\ W(i)0 \end{array}$ | , ,     |           | i)1 $(i)1$  | $ \begin{array}{c} R(i)1, \ W(i) \\ R(i)1, \ W(i) \\ R(i)1, \ W(i) \\ \vdots \\ R(i)1, \ W(i) \\ \end{array} $ | i)0 $(i)0$ | $R(i)0, W(i)1 \\ R(i)0, W(i)1 \\ R(i)0, W(i)1 \\ \vdots \\ R(i)0, W(i)1$ |  |  |

|                                                             | March 4                                                                   |         |           | N           | Iarch 1a                                                                                                       |            | March 2a                                                                 |  |  |

| $0$ $1$ $2$ $\vdots$ $N-1$                                  | $R(i)1, W(i)0 \\ R(i)1, W(i)0 \\ R(i)1, W(i)0 \\ \vdots \\ R(i)1, W(i)0$  |         | Wartezeit | R(i) $R(i)$ | 0, W(i)1<br>0, W(i)1<br>0, W(i)1<br>0, W(i)1<br>0, W(i)1                                                       | Wartezeit  | $R(i)1$ $R(i)1$ $R(i)1$ $\vdots$ $R(i)1$                                 |  |  |

- Mehrfaches Durchwandern des Speichers mit der Operationsfolge Zelle Lesen, Wert kontrollieren, inversen Wert zurückschreiben.

- Umkehrung der Adressierungsreihenfolge, um Überkopplungen in beiden Richtungen nachzuweisen.

- Wartezeit für den Nachweis von Datenhalteproblemen.

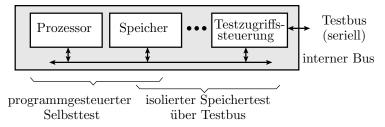

## 6.69 Test eingebetteter Blockspeicher

Eingebettete Blockspeicher werden vorzugsweise isoliert von ihrer Schaltungsumgebung getestet:

- über herausgezogene Bussignale,

- über den Testbus oder

- programmgesteuert vom Prozessor als eingebauter Selbsttest.

## Zusammenfassung

#### 6.70 Gezielte Testsuche

- Gezielte Testsuche beginnt in der Regel mit einer Fehlersimulation mit zufälligen Eingaben und Abhaken der nachweisbaren Fehler bzw. Zählen der Nachweisanzahl.

- Zur Fehlersimulation werden die logischen Berechnung in Maschinenbefehlsfolgen übersetzt und bitparallel ausgeführt. Die Simulation größerer Funktionsbausteine mit tausenden von Fehlern und millionen von Tests kann dennoch Tage dauern.

- Für die geziele Suche haben wir den D-Algoritmus kennen gelernt. Er treibt vom Fehlerort Beobachtungspfade zu Augängen und Steuerpfade zu Eingängen.

- Mit den Mehrdeutigkeiten bei der Pfadsensibilisierung wird ein Suchbaum aufgebaut und bei Wiedersprüchen immer zum letzten Ast mit noch nicht durchmusterten Alternativen zurückgekehrt.

- Widerspruch und keine weitere Alternative weist einen Modellfehler als redundant aus, d.h. Redundanznachweis aufwändiger, als existierende Tests zu finden

## 6.71 Heuristiken zur Erhöhung des Sucherfolgs

- Frühe Widerspruchserkennung durch Implikationstests.

- Suchraumbegrenzung auf unabhängig steuerbare Eingänge.

- Bevorzugung erfolgsversprechenderer Entscheidungen z.B. anhand geschätzter Wahrscheinlichkeiten für die Steuer- und Beobachtbarkeit.

- Beibehaltung komplexer Teilfunktionen als Wertetabellen statt Nachbildung durch Gatter.

## 6.72 Sequentielle Schaltungen

- Sequentielle Schaltungen werden für die Testsuche zu einer pseudo-kombinatorischen Ersatzschaltung aufgerollt.

- Solange gespeicherte Werte nicht auf Eingänge der kombinatorischen Verarbeitung rückgeführt werden,

Testberechung wie für Schaltungen ohne Speicherzellen.

- Rückführung erschweren die Testsuche und mindern die Erfolgsrate, Tests zu finden.

- Problemvermeidung durch Schreib-/Lesezugriff auf interne Speicherzellen über Scan-Register.

## 6.73 Speicher

- Für Speicher und andere regelmäßig strukturierte Schaltungen gibt es sog. C-Tests. Das sind parametrierte auf unterschiedliche Größe und Konfigurationen anpassbare Testsatzalgorithmen, die für jede Zelle alle Modellfehler nachweisen.

- Der Marching-Algorithmus für RAM durchläuft beispielsweise alle Adressen vor- und rückwärts und führt dabei bestimmte Zugriffsoperationen aus.

# Selbsttest

### 3. Selbsttest

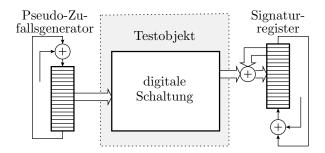

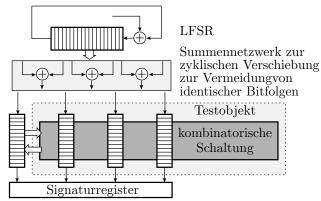

#### 6.74 Selbsttest

Selbsttestfunktionen für digitale Schaltungen werden realisiert durch Erweiterung der Testobjekte um:

- Pseudo-Zufallsgeneratoren an den Eingängen, vorzugsweise LFSR (Linear Feedback Shift Register), Zähler, ...

- Signaturegister oder anderer Überwachungsfunktionen an den Ausgängen und

- eine Steuerung für den Testablauf:

- Initialisierung Testmustergenerator, Prüfkennzeichen, Testobjekt

- Wiederhole für alle Testschritte

- Testmustergenerator weiterschalten,

- Bildung der Schaltungsausgaben aus den Testeingaben,

- Weiterschalten Signaturregister oder andere Kontrolle.

- Steuerung und Abfrage Prüfkennzeichen und anderer Kontrollergebnisse über seriellen Testbus (Folie 5.40).

Vorteile gegenüber externer Prüftechnik:

- sehr viele Tests mit voller Systemgeschwindigkeit,

- auch in der Einsatzphase als Einschalt- oder Wartungstest, ...

## Pseudo-Zufallsregister

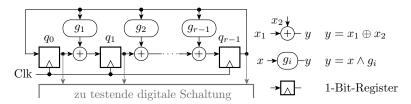

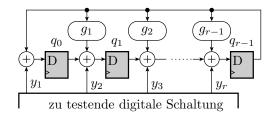

## 6.75 Linear rückgekoppelte Schieberegister

In einer ersten Ausführung verschiebt ein linear rückgekoppelte Schieberegister (LFSR Linear Feeback Shift Register) seinen r-Bit-Zustand  $\mathbf{s} = (s_{r-1}, s_{r-2}, \dots, s_0)$  um eine Stelle nach links und addiert, wenn das herausgeschobene Bit  $s_{r-1}$  gleich »1 « ist, eine Bitvektorkonstante  $\mathbf{g} = (g_{r-1}, g_{r-1}, \dots, g_1, 1)$  zum Zustand **s.**

Konstanteneliminition entfernt in der Schaltung die EXOR mit  $q_i = 0$ .

Für jede Bitanzahl r des Zustandsvektors gibt es Konstantenvektoren g, sog. »primitive Polynome«, bei denen alle Zustände außer 000...0 in einander übergehen (Folie 5.60 ff.). Diese werden bevorzugt.

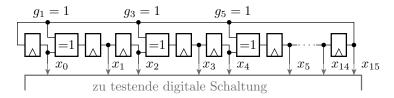

### 6.76 Primitive Polynome und die Konstante g

Mit dem Internet-Suchbegriff »Primitive Polynome« findet man z.B. für 16-Bit LFSR:

$$z^{16} \oplus z^5 \oplus z^3 \oplus z \oplus 1$$

Das bedeutet  $g_1=g_3=g_5=1$  und alle anderen  $g_i|_{i\not\in\{1,3,5\}}=0$ . In Realisierung als Digitalschaltung für  $g_i=1$  EXOR-Gatter einfügen und für  $g_i=0$  EXOR-Gatter weglassen.  $g_0$  und  $g_r$  sind immer 1.

$z^i$  Operator für eine Verschiebung um i Bitstellen.

$g_i, q_i$  Registerbits und Rückführkoeffizienten des LFSR.

r Bitanzahl des linear rückgekoppelten Schieberegisters.

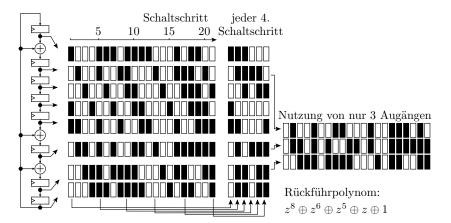

## 6.77 Pseudo-Zufallsfolge eines 8-Bit-LFSR

Falls die »Streifenmuster« durch die Schiebeoperationen stören, z.B. für Verzögerungsfehlernachweis, nur einen Teil der Ausgaben nutzen.

## 6.78 LFSR mit zentraler Rückführung

Statt Ausgang auf mehrere Bits, Rückkopplung mehrere Bits auf den Eingang. Bei gleichen Rückführstellen haben LFSR mit zentraler und dezentraler Rückführung gleiche Zyklusstruktur.

#### 6.79 Zellenautomaten

- Folgebit gleich EXOR Nachbarbits optional plus eigener Bitwert.

- Mir ausgewälte Toggle-Zellenzuordnungen Maximalzyklus  $2^r 1$ .

## Signaturregister

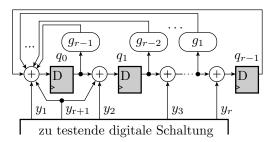

#### 6.80 Paralles Signaturregister

EXOR mit  $g_1 = 0$ oder  $x_i = 0$  entfallen durch Konstantenelimination auch mehr als rEingänge

Für die Bildung auf Prüfkennzeichen ist es nur wichtig, dass die Abbildung pseudo-zufällig hinsichtlich der zu erwartenden Verfälschungen erfolgt. Diese Eigenschaft hat auch ein rückgekoppeltes Schieberegister, bei dem die Daten modulo-2 als Bitvektoren zu den Registerzuständen addiert werden (paralleles Signaturregister, Folie 5.60 ff.) .

- $y_i$  Testobjektausgang i. r Registerlänge.

- r Registerlange

## 6.81 Dezentrale Rückführung auch ok

- Autonome Zyklusstruktur bei gleichen Rückführkoeffizienten  $g_i$  für zentrale und dezentrale Rückführung gleich.

- Für Signaturregister werden, wie für Pseudo-Zufallsgeneratoren auch, primitive Rückkopplungen bevorzugt, bei denen bei  $x_i = 0$  alle Zustände  $\mathbf{q} \neq 00 \dots 0$  zyklisch durchlaufen werden.

- Keine primitive Rückführung bedeutet aber nicht, dass dann die Fehlermaskierungswahrscheinlichkeit signifikant größer  $2^{-r}$  ist.

Registerbits und Rückführkoeffizienten des LFSR. Testobjektausgang *i*.

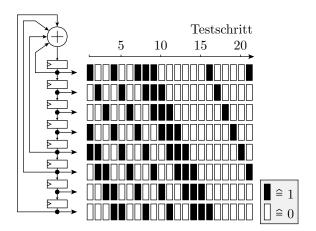

## 6.82 Experiment Maskierungswahrscheinlichkeit

Ein Signaturregister maskiert verfälschte Testausgabedaten durch Abbildung auf die Sollsignatur mit einer Wahrscheinlichkeit von:

$$p_{\rm M} = 2^{-r}$$

(vergl. Gl. 1.35). Wegen der geringen Eintrittswahrscheinlichkeit sollte die Anzahl der Maskierungen X poisson-verteilt sein:

mit dem Erwartungswert  $\lambda = \#F_D \cdot 2^{-r}$ .

Kontrolle der Verteilung der Fehlermaskierung mit  $\lambda = 250 \cdot 2^{-6} = 3.9$ :

- Simulation einer 4-Bit-ALU mit einem Testsatz, der alle 250 unterstellten Haftfehler erkennt.

- Zählen der Maskierungen durch ein 6-Bit Signaturregister.

- für 96 Kombination der Testanordnung.

$p_{

m M}$  Maskierungswahrscheinlichkeit (Mask probability). # $F_{

m D}$  Anzahl der vom Testsatz nachweisbaren Fehler.

Anzahl von den # $F_D = 96$  Fehlern, die vom Signaturregister maskiert werden.

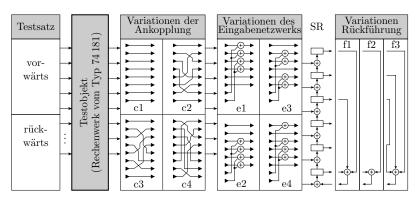

#### 6.83 Testanordnungen

96 Testanordnungen durch Kombination:  $(2 \cdot 4 \cdot 4 \cdot 3 = 96)$

- vor-/rückwärts: Varianten der Testreihenfolge

- c1 bis c4: Varianten für eine 8 auf 8 Eingabezuordnung,

- e1 bis e4: Varianten für eine 8 auf 6 Bit EXOR-Zusammenfassung,

- fb1 bis fb3: Rückführungen (f1 und f3 zufällig gewählt, f2 primitiv).

## 6.84 Anzahl der Maskierungen

#### Experimentell bestimme Anzahl der Maskierungen *k*:

|       |    | e1       |   |   | e2       |   |   | e3       |   |   |          | e4 |   |   |   |   |   |

|-------|----|----------|---|---|----------|---|---|----------|---|---|----------|----|---|---|---|---|---|

|       |    | c1c2c3c4 |   |   | c1c2c3c4 |   |   | c1c2c3c4 |   |   | c1c2c3c4 |    |   |   |   |   |   |

| vor-  | f1 | 3        | 4 | 1 | 2        | 3 | 4 | 3        | 3 | 4 | 2        | 4  | 3 | 4 | 3 | 4 | 6 |

|       | f2 | 3        | 4 | 1 | 7        | 2 | 2 | 1        | 4 | 2 | 1        | 1  | 3 | 2 | 5 | 3 | 7 |

|       | f3 | 5        | 2 | 2 | 8        | 4 | 5 | 3        | 4 | 3 | 6        | 3  | 7 | 5 | 3 | 3 | 4 |

|       | fb | 6        | 4 | 4 | 2        | 3 | 4 | 3        | 4 | 3 | 4        | 3  | 4 | 4 | 8 | 4 | 5 |

| rück- | f2 | 2        | 0 | 0 | 1        | 4 | 1 | 4        | 1 | 0 | 0        | 0  | 1 | 1 | 1 | 4 | 1 |

| wärts | f3 | 2        | 4 | 3 | 4        | 4 | 8 | 5        | 8 | 3 | 3        | 3  | 6 | 3 | 3 | 4 | 3 |

| k                                          | 0   | 1   | 2    | 3    | 4    | 5    | 6   | 7   |

|--------------------------------------------|-----|-----|------|------|------|------|-----|-----|

| $96 \cdot e^{-3.9} \cdot \frac{3.9^k}{k!}$ | 1,3 | 7,5 | 14,7 | 19,2 | 18,7 | 14,6 | 9,5 | 5,3 |

| Experiment                                 | 5   | 12  | 11   | 25   | 26   | 6    | 4   | 3   |

- Für nur 96 verschiedene Testanordnungen gute Übereinstimmung.

- Keine auffällig gute oder schlechte Testanordnung.

- Zufällig gewählte Rückführung nicht schlechter als primitive.

#### Selbsttest mit LFSR

#### 6.85 Selbsttest mit LFSR

- Einrahmen der Schaltung mit Schieberegistern und Ergänzung von EXOR-Gattern für Rückführungen und SR-Eingänge.

- Init-Wert und Rückführung für Pseudo-Zufallsgenerator so wählen, dass sich keine Testeingabefolgen wiederholen.

- Wenn als Schieberegister vorhandene Ein- und Ausgaberegister verwendet werden, besonders niedriger Zusatzaufwand.

- Test mit voller Schaltungsgeschwindigkeit von Millionen bis Milliarden Tests pro Sekunde.

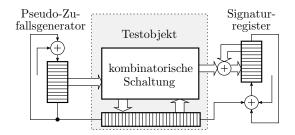

## 6.86 Selbsttest mit LFSR und Scan-Registern

- Ersatz interner Speicherzellen, vor allem solche, die Zustände speichern, durch Scan-Register.

- Zwischen den Testschritten wird das Scan-Register seriell in das Signaturregister auslesen und neu beschreiben.

- Lese- und Schreibzugriff auf die Zustandsspeicher reduzieren die erforderliche Testsatzlänge für dieselbe Fehlerüberdeckung.

- Insgesamt kann sich die erforderliche Testzeit sogar verkürzen.

Für sehr große Systeme, z.B. Multi-Chip-Module auch mehrere Scan-Register, die zwischen den Testschritten parallel gelesen und mit neuen Zufallswerten beschrieben werden.

Die EXOR-Summen mehrerer LFSR-Bits ergeben dieselbe Folge, nur zyklisch verschoben [Ke07].

[Ke07] G. Kemnitz: Test und Verläßlichkeit von Rechnern. Springer 2007.

## Fehlerorientierte Wichtung

#### 6.88 Fehlerorientierte Wichtung

Wenn mit akzeptabler Testsatzlänge nicht genug Modellfehler nachgewiesen werden, kann eine fehlerorientierte Wichtung helfen.

#### Wichtung und Beobachtbarkeit eines Bits $x_i$ :

Wichtung ist die Auftrittswahrscheinlichkeit von Signalwert  $x_i = 1$ .

$$g\left(x_{i}\right) = \mathbb{P}\left(x_{i} = 1\right)$$

Beobachtbarkeit ist die Wahrscheinlichkeit, dass eine fehlerverursachte Invertierung eines Bits  $x_i$  mindestens ein Ausgabebit  $y_i$  verfälscht.

Geänderte Eingabewichtungen ändern die Wichtungen und Beobachtbarkeiten interner Signale und darüber die Fehlfunktionsraten der einzelnen Fehler zum Teil erheblich.

Man kann Wichtung auch als Operationsprofil betrachten (Abschn. 3.2.4).

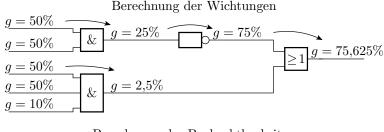

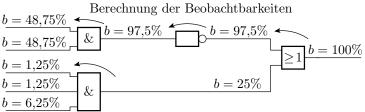

#### 6.89 Wichtungen und Beobachtbarkeit

Die Wichtung einer UND-Verknüpfung ist das Produkt der Wichtungen der Operanden. ... Die Eingabe einer UND-Operation ist beobachtbar, wenn die andere Eingabe eins ist, ...

$$x_{1} \xrightarrow{g(x_{1}), b(x_{1})} & b(x_{2}) = b(y) \cdot g(x_{1}) \\ x_{2} \xrightarrow{g(x_{2}), b(x_{2})} & b(x_{1}) = b(y) \cdot g(x_{2}) \\ x_{1} \xrightarrow{g(x_{1}), b(x_{1})} & g(y) = g(x_{1}) \cdot g(x_{2}) \\ x_{2} \xrightarrow{g(x_{2}), b(x_{2})} & b(x_{1}) = b(y) \cdot (1 - g(x_{2})) \\ x_{2} \xrightarrow{g(x_{2}), b(x_{2})} & b(x_{2}) = b(y) \cdot (1 - g(x_{1})) \\ x_{2} \xrightarrow{g(x_{2}), b(x_{2})} & g(y) = 1 - (1 - g(x_{1})) \cdot (1 - g(x_{2})) \\ x \xrightarrow{g(x_{2}), b(x_{2})} & g(y) = (1 - g(x_{2})) \\ x \xrightarrow{g(x_{2}), b(x_{2})} & g(y) = (1 - g(x_{2})) \\ x \xrightarrow{g(x_{2}), b(x_{2})} & g(y) = (1 - g(x_{2})) \\ x \xrightarrow{g(x_{2}), b(x_{2})} & g(y) = (1 - g(x_{2})) \\ x \xrightarrow{g(x_{2}), b(x_{2})} & g(y) = (1 - g(x_{2})) \\ x \xrightarrow{g(x_{2}), b(x_{2})} & g(y) = (1 - g(x_{2})) \\ x \xrightarrow{g(x_{2}), b(x_{2})} & g(y) = (1 - g(x_{2})) \\ x \xrightarrow{g(x_{2}), b(x_{2})} & g(y) = (1 - g(x_{2})) \\ y \xrightarrow{g(x_{2}), b(x_{2})} & g(y) = (1 - g(x_{2})) \\ y \xrightarrow{g(x_{2}), b(x_{2})} & g(y) = (1 - g(x_{2})) \\ y \xrightarrow{g(x_{2}), b(x_{2})} & g(y) = (1 - g(x_{2})) \\ y \xrightarrow{g(x_{2}), b(x_{2})} & g(y) = (1 - g(x_{2})) \\ y \xrightarrow{g(x_{2}), b(x_{2})} & g(y) = (1 - g(x_{2})) \\ y \xrightarrow{g(x_{2}), b(x_{2})} & g(y) = (1 - g(x_{2})) \\ y \xrightarrow{g(x_{2}), b(x_{2})} & g(y) = (1 - g(x_{2})) \\ y \xrightarrow{g(x_{2}), b(x_{2})} & g(y) = (1 - g(x_{2})) \\ y \xrightarrow{g(x_{2}), b(x_{2})} & g(y) = (1 - g(x_{2})) \\ y \xrightarrow{g(x_{2}), b(x_{2})} & g(y) = (1 - g(x_{2})) \\ y \xrightarrow{g(x_{2}), b(x_{2})} & g(y) = (1 - g(x_{2})) \\ y \xrightarrow{g(x_{2}), b(x_{2})} & g(y) = (1 - g(x_{2})) \\ y \xrightarrow{g(x_{2}), b(x_{2})} & g(y) = (1 - g(x_{2})) \\ y \xrightarrow{g(x_{2}), b(x_{2})} & g(y) = (1 - g(x_{2})) \\ y \xrightarrow{g(x_{2}), b(x_{2})} & g(y) = (1 - g(x_{2})) \\ y \xrightarrow{g(x_{2}), b(x_{2})} & g(y) = (1 - g(x_{2})) \\ y \xrightarrow{g(x_{2}), b(x_{2})} & g(y) = (1 - g(x_{2})) \\ y \xrightarrow{g(x_{2}), b(x_{2})} & g(y) = (1 - g(x_{2})) \\ y \xrightarrow{g(x_{2}), b(x_{2})} & g(y) = (1 - g(x_{2})) \\ y \xrightarrow{g(x_{2}), b(x_{2})} & g(y) = (1 - g(x_{2})) \\ y \xrightarrow{g(x_{2}), b(x_{2})} & g(y) = (1 - g(x_{2})) \\ y \xrightarrow{g(x_{2}), b(x_{2})} & g(y) = (1 - g(x_{2})) \\ y \xrightarrow{g(x_{2}), b(x_{2})} & g(y) = (1 - g(x_{2})) \\ y \xrightarrow{g(x_{2}), b(x_{2})} & g(y) = (1 - g(x_{2})) \\ y \xrightarrow{g(x_{2}), b(x_{2})} & g(y) = (1 - g(x_{2})) \\ y \xrightarrow{g(x_{2})$$

Wichtungen werden in Richtung und Beobachtbarkeiten entgegen der Richtung des Berechnungsflusses bestimmt.

Prof. G. Kemnitz · Institut für Informatik, TU Clausthal

g(...) Wichtung, Auftrittshäufigkeit des Signalwerts 1.

b(...) Beobachtbarkeit, Wahrscheinlichkeit, das eine Invertierung ein Ausgabebit ändert.

#### 4. Fehlerorientierte Wichtung

#### Berechnung der Nachweiswahrscheinlichkeiten:

$$p_{\text{sa0}}(x_i) = b(x_i) \cdot g(x_i)$$

$$p_{\text{sa1}}(x_i) = b(x_i) \cdot (1 - g(x_i))$$

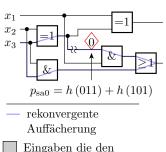

#### 6.91 Rekonvergente Auffächerung

Bei rekonvergenter Auffächerung werden abhängige Zufallswerte log. verknüpft, so dass die einfachen Regel für  $\mathbb{P}(A \land B)$  etc. nicht gelten.

Berechnung der Nachweiswahrscheinlichkeiten über Wertetabellen:

| Eingaben die den  |

|-------------------|

| Fehler nachweisen |

| 1 | Eingabe       | Ausg.      | $h(\mathbf{x})$ | für $g(x)$ | $_{i})=g$ |

|---|---------------|------------|-----------------|------------|-----------|

| ı | $x_3 x_2 x_1$ | $y_2  y_1$ | g = 0.5         | g = 0.3    | g=0,7     |

|   | 0 0 0         | 0 0        | 0,125           | 0,343      | 0,027     |

| 2 | 0 0 1         | 0 1        | 0,125           | 0,147      | 0,036     |

|   | 0 1 0         | 0 1        | 0,125           | 0,147      | 0,036     |

|   | 0 1 1         | 1 0        | 0,125           | 0,036      | 0,147     |

|   | 1 0 0         | 0 1        | 0,125           | 0,147      | 0,036     |

|   | 1 0 1         | 1 0        | 0,125           | 0,036      | 0,147     |

|   | 1 1 0         | 1 0        | 0,125           | 0,036      | 0,147     |

|   | 1 1 1         | 1 1        | 0,125           | 0,027      | 0,343     |

|   |               |            |                 |            |           |

$p_{\rm sa0}: 0.25 \quad 0.072 \quad 0.294$

$x_i, y_i$  Eingabe- und Ausgabesignale.

g Wichtung der Eingabesignale  $x_1$ ,  $x_2$  und  $x_3$ .

$h\left(\mathbf{x}\right)$  Auftrittshäufigkeit des Eingabevektors  $x_3x_2x_1$ .

#### 6.92 Fehlerabdeckung und Wichtung

Nachweiswahrscheinlichkeiten für  $g(x_i) = g$ :

$\bullet$ der 64 sa<br/>1-Fehler

$$p_{\text{sa1}}(1) = g^{63} \cdot (1 - g)$$

$$p_{\text{sa1}}(N) = 1 - e^{-g^{63} \cdot (1 - g) \cdot N}$$

• des einen sa0-Fehlers

$$p_{\text{sa0}}(1) = g^{64}$$

$p_{\text{sa0}}(N) = 1 - e^{-g^{64} \cdot N}$

Zu erwartende Fehlerabdeckung als Mittelwert der Nachweiswahrscheinlichkeiten aller 65 Haftfehler:

$$\mu_{\text{FC}}(N) = 1 - \frac{64 \cdot e^{-g^{63} \cdot (1-g) \cdot N} + e^{-g^{64} \cdot N}}{65}$$

g Wichtung der Eingabesignale  $x_1$  bis  $x_64$ .

N Anzahl der Tests.

$\mu_{\mathrm{FC}}\left(N\right)$  Zu erwartende Fehlerabdeckung in Abhängigkeit von der Testanzahl.

$$\mu_{FC} (N = 10^{6}) = 1 - \frac{64 \cdot e^{-g^{63} \cdot (1-g) \cdot 10^{6}} + e^{-g^{64} \cdot 10^{6}}}{65}$$

$$\mu_{FC} (N = 10^{6}) \begin{vmatrix} 100\% \\ 80\% \\ 60\% \\ 20\% \end{vmatrix}$$

0,76

0,8

0,84

q

Eine Erhöhung der Wichtung an allen Eingängen von  $g \le 76\%$  auf  $g \ge 86\%$  erhöht die Fehlerabdeckung für  $N=10^6$  Tests von 0 auf 1.

Allgemein sind zur Erzielung einer hohen Fehlerabdeckung die Wichtungen  $g\left(x_{i}\right)$  für alle Eingänge  $x_{i}$  individuell anzupassen.

g Wichtung der Eingabesignale  $x_1$  bis  $x_64$ .

N Anzahl der Tests.

$\mu_{\mathrm{FC}}\left(N\right)$  Zu erwartende Fehlerabdeckung in Abhängigkeit von der Testanzahl.

### 6.95 Fehlerorientierte Wichtungsauswahl

#### Pragmatischer Ansatz aus [HaK93]:

- Zusammenstellung der Haftfehlermenge.

- **2** Längerer Zufallstest, z.B.  $N=10^6$  und Abhaken aller damit nachweisbaren Modellfehler.

- Gezielte Berechnung von Tests für die übrigen Modellfehler. Eingabebits, die für den Fehlernachweis keinen bestimmten Wert haben müssen, bleiben »X«,

- Festlegung der Wichtung so, dass die gefundenen Tests bevorzugt erzeugt werden.

- Längerer gewichteter Zufallstest, z.B. auch wieder  $N=10^6$ , und auch wieder Abhaken aller damit nachweisbaren Modellfehler.

- Wenn immer nach nicht alle Modellfehler nachweisbar sind, Wiederholung von Schritt 4 und 5.

Anzahl der Tests.

[HaK93] J. Hartmann, G. Kemnitz: How to do weighted random testing for BIST? ICCAD 1993.

#### 4. Fehlerorientierte Wichtung

Zur Schaltungsminimierung des Testmustergenerators ist eine Beschränkung auf nur 5 verschiedene Wichtungswerte zweckmäßig:

$$g\left(x_{i}\right) = \begin{cases} 0 & \text{wenn } \forall x_{i.j} \in \{0, \mathbf{X}\} \\ 1 & \text{sonst wenn } \forall x_{i.j} \in \{1, \mathbf{X}\} \\ 2^{-m_{\mathrm{AND}}} & \text{sonst wenn } \#0 \gg \#1 \\ 1 - 2^{-m_{\mathrm{AND}}} & \text{sonst wenn } \#0 \ll \#1 \\ 0,5 & \text{sonst} \end{cases}$$

Beispiel für  $m_{\text{AND}} = 3$ :

| Test        | vektor | : 1 | 2            | 3            | 4 | 5 | 6 | 7            | 8            | 9 | 10           | 11 | $g(x_i)$     |

|-------------|--------|-----|--------------|--------------|---|---|---|--------------|--------------|---|--------------|----|--------------|

| <u>:</u> :: | $x_1$  | 1   | $\mathbf{X}$ | 0            | 1 | 0 | 0 | $\mathbf{X}$ | 1            | 0 | 1            | 1  | 0,5          |

| ep          | $x_2$  | 1   | 1            | X            | 1 | 1 | X | 1            | X            | X | $\mathbf{X}$ | Χ  | 1            |

| gar         | $x_3$  | 0   | 0            | 1            | 0 | 0 | Х | 0            | Х            | 1 | 0            | 0  | $2^{-3}$     |

| 볊           | $x_4$  | 1   | 0            | $\mathbf{X}$ | 0 | Х | 0 | 1            | $\mathbf{X}$ | 1 | $\mathbf{X}$ | 0  | 0,5          |

| ~           | $x_5$  | 1   | 1            | 1            | Х | 0 | 1 | 1            | 1            | Х | 0            | 1  | $1 - 2^{-3}$ |

X Signalwert ungültig oder für den Fehlernachweis ohne Bedeutung.

#0 Anzahl der Nullen im Testsatz für Eingang i des Testobjekts.

#1 Anzahl der Einsen im Testsatz für Eingang i des Testobjekts.  $m_{\mathrm{AND}}$  Anzahl UND-verknüpfter ungewichteter Bits für die Wichtung  $0 < q \ll 0,5$ .

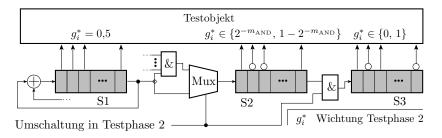

#### 6.97 Implementierung als Selbsttest

- Testphase 1: Erzeugung ungewichteter Pseudo-Zufallseingaben mit LFSR S1. Serielle Weitergabe an die Schiebereg. S2 und S3.

- Testphase 2: Verringerung der Wichtung

- $\blacksquare$  in S2 durch UND-Verknüpfung von  $m_{\rm AND}$  Ausgabefolgen von S1 und für S2 und

- in S3 durch »UND 0«.

Erzeugung  $g(x_i) = 1 - 2^{-m_{\text{AND}}}$ ,  $g(x_i) = 1$  durch Inverierung.

Kaum aufwändiger als Selbstest nur mit ungewichtetem Zufallswerten.

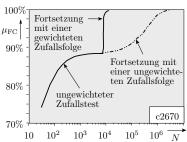

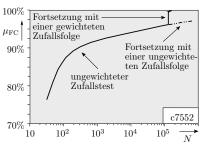

#### 6.98 Beispielentwurf mit ISCAS-Benchmarks

- Test mit 10<sup>4</sup> bzw. 10<sup>5</sup> ungewichteten Zufallsmustern, die 90% bzw. 95% der Haftfehler nachweisen.

- Gezielte Testberechnung für die restlichen Haftfehler.

- Individuelle Wichtung aller Eingabebits zur Maximierung der mittleren Auftrittshäufigkeit der berechneten Testeingaben.

- Weitere 10<sup>4</sup> bzw. 10<sup>5</sup> gewichtet Zufallstests weisen alle verbleibenden nichtredundanten Modellfehler nach.

$\mu_{\rm FC}$ , N Zu erwartende Haftfehlerabdeckung, Testanzahl.

#### **RAM-Selbsttest**

#### 6.99 Marching-Test für RAM (Folie 6.67)

| $\mathop{\mathrm{Adresse}}_{i}$ | Initiali-<br>sierung                             | March 1                                                                                       |           |             | March                                                                                                      | 2          | March 3                                                                  |

|---------------------------------|--------------------------------------------------|-----------------------------------------------------------------------------------------------|-----------|-------------|------------------------------------------------------------------------------------------------------------|------------|--------------------------------------------------------------------------|

| $0 \\ 1 \\ 2 \\ \vdots \\ N-1$  |                                                  | $\begin{array}{c} R(i)0,W(i)1\\ R(i)0,W(i)1\\ R(i)0,W(i)1\\ \vdots\\ R(i)0,W(i)1 \end{array}$ |           |             | $ \begin{array}{c} R(i)1,  W(i) \\ R(i)1,  W(i) \\ R(i)1,  W(i) \\ \vdots \\ R(i)1,  W(i) \\ \end{array} $ | i)0 $(i)0$ | $R(i)0, W(i)1 \\ R(i)0, W(i)1 \\ R(i)0, W(i)1 \\ \vdots \\ R(i)0, W(i)1$ |

|                                 | March                                            | 4 N                                                                                           |           |             | Iarch 1a                                                                                                   |            | March 2a                                                                 |

| $0 \\ 1 \\ 2 \\ \vdots \\ N-1$  | R(i)1, R(i)1, W $R(i)1, W$ $R(i)1, W$ $R(i)1, W$ | V(i)0 $V(i)0$                                                                                 | Wartezeit | R(i) $R(i)$ | 0, W(i)1<br>0, W(i)1<br>0, W(i)1<br>0, W(i)1<br>0, W(i)1                                                   | Wartezeit  | $R(i)1$ $R(i)1$ $R(i)1$ $\vdots$ $R(i)1$                                 |

Die Testeingabebereitstellung und -auswertung vorlangt einen Vor-/Rückwärtszähler und eine kleine Steuerung, die Zählrichtung, Schreibwert und Soll-Lese-Wert auswählt. Wartezeiten können von außen über den Testbus gesteuert werden.

## Zusammenfassung

#### 6.100 Selbsttest digtaler Schalkreise

- Ergänzung von Pseudo-Zufassgeneratoren an den Eingängen, in der Regel LFSR, für die Durchführung langer Zufallstests und Signaturregistern an den Ausgängen.

- Für die Testmustergeneratoren sind die Rückführungen und Startwerte so zu wählen, dass nicht mehrfach dieselbe Testfolge wiederholt wird und die Musterabhängigkeiten den Fehlernachweis nicht stören (bevorzugt primitive Rückführungen).

- Die Signaturregister sind so zu wählen, dass die Maskierungswahrscheinlichkeit z.B. durch falsche Rückführung den Wert  $2^{-r}$  nicht übersteigt. Ein Experiment hat gezeigt, dass man da nicht viel falsch machen kann.

- Zur Verbesserung der Fehlerabdeckung werden auch interne Speicherzellen zu Scan-Registern zusammengefasst, die zwischen den Testschritten in das Signaturregister ausgelesen und mit neuen Pseudo-Zufallswerten beschrieben werden.

#### 6.101 Fehlerorientierte Wichtung und RAM

- Wenn die Fehlerabdeckung mit  $N=10^{6...9}$  Zufallstests nicht ausreicht, gibt es auch die Möglichkeit, in weiteren Testphasen die Auftrittshäufigkeiten der Nullen und Einsen an den Testobjekteingängen so anzupassen, dass die mit ungewichteten Zufallsmustern zu schlecht nachweisbaren Fehler bevorzugt nachgewiesen werden.

- Dazu werden im einfachten Fall für alle in der ersten Testphase mit ungewichteten Zufallswerten nicht nachweisbaren Modellfehler Tests gesucht und die Wichtungen an die Häufigkeiten der Nullen und Einsen im gefundenen Testsatz angepasst.

- Für regelmäßig strukturierte Schaltungen wie RAM gibt es oft einfachere Lösungen mit exzellenter Fehlerabdeckung. Als Beispiel wurde die Implementierung eines Marching Tests für einen RAM-Block skizziert.

#### 6.102 Hierarchischer Test der Hardware

Rechnerhardware besteht aus tauschbaren Komponenten:

- tauschbare Teilsysteme.

- tauschbare Leiterplatten,

- austauschbare Bauteile.

Die Komponenten werden vor Einbau in das übergeordnete System gründlich getestet.

#### Wiederholungsfragen

- Warum tauschbare Komponenten bzw. unter welcher Bedingung nicht erforderlich (nicht zweckmäßig)?

- Warum ist ein gründlicher Komponententest zu fordern?

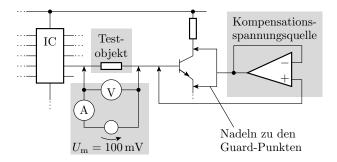

#### 6.103 Leiterplattentest (Folie 2.39)

Hauptfehler auf Baugruppen sind Kurzschlüsse und Unterbrechungen. Nachweis durch Widerstandsmessungen zwischen und entlang der Verbindungen.

In der Serienfertigung erfolgt die Kontaktierung mit einem mit Unterdruck angesaugten Nadeladapter.

Die Nadeln sind mit einer Relais-Matrix verbunden, über die vom Testprogramm Prüfgeräten angeschlossen werden. Auch Bestückungsfehler lassen sich überwiegend mit Zweipunktmessungen von Strom-Spannungsbeziehungen erkennen. Fehlerlokalisierung im Vergleich zur Rückverfolgung falsche Ausgaben von dynamischen Tests sehr einfach (vergl. Abschn. 2.1.2).

#### 6.104 Zweipunktmessung Bestückungkontrolle

Kontrolle auf Bestückungsfehler durch Überprüfung ausgewählter Zweipunktmerkmale:

- Widerstandswerte.

- Kapazitäten,

- Flussspannungen von Dioden, ...

Verbindungskontrolle IC-Anschlüsse zu den Kontakt-Pads durch Ausmessen der Schutzdioden zur Versorgungsspannung oder Masse.

#### 6.105 Analoger In-Circuit Test

Die Strom-Spannungs-Beziehung zwischen zwei Punkten hängt nicht nur vom Bauteil zwischen den Nadeln, sondern von allen Strompfaden, im Beispiel durch Transistor und Schaltkreis ab.

Unterdrückung von Parallelströmen zum Testobjekt durch Kompensation der Spannungsabfälle über den wegführenden Bauteilen auf einer Testobjektseite auf null über »Guard-Punkte«:

Unterdrückung von Parallelströmen zum Testobjekt durch Kompensation der Spannungsabfälle über den wegführenden Bauteilen auf einer Testobjektseite auf null über »Guard-Punkte«:

- Vereinfacht die Testprogrammerstellung und Fehlerlokalisierung, insbesonderen die Sollwert- und Sollwerttoleranzfestlegung.

- Mindert die Häufigkeit von Fehlklassifikationen.

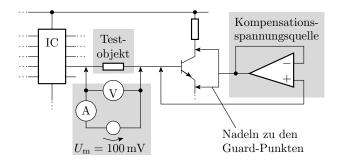

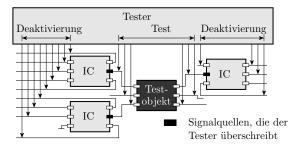

#### 6.106 Digitaler In-Circuit-Test

- Kontaktierung der Baugruppe über ein Nadelbetadapter.

- Isolierter Test der Schaltkreise durch Überschreiben der digitalen Schaltkreiseeingaben mit stromstarken Treibern.

- Im Gegensatz zum analogen ICT unter Spannung.

- Andere Schaltkreise möglichst deaktivieren (Ausgänge trennen).

Erlaubt auch den isolierten Test der Bausteine, aber im Gegesatz zum analogen In-Circuit-Test unter Spannung.

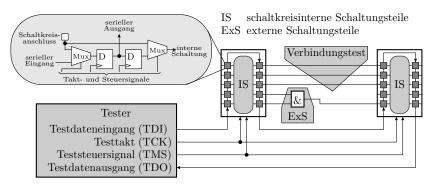

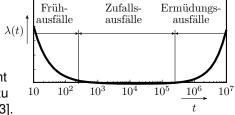

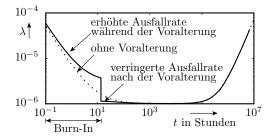

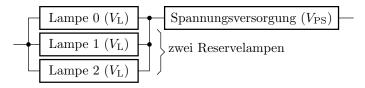

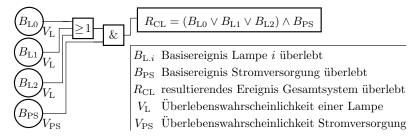

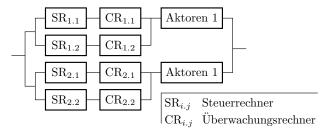

#### 6.107 Boundary-Scan (Folie 5.38)